mindhacker

New Member

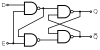

I am about to make a perfect D flip-flop out of simple gates. I used 74ls00 as illustrated in the diagram. It works perfectly alone but when i connect its input to a circuit it started to work incorrectly. Example is this. I connect its Q' to its D input. Q is supposed to be 0 then 1 then 0....but it works indefinitely. As if it is in undefined state What causes this? How can I fix it?