Shadow_warrior

Member

Hello people!

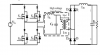

I am trying to find a gate driver for IGBTs for a current-source full bridge topology. The main difference between current-fed and normal voltage-fed converters is that due to a boost inductance at the input, there should always be a path of current flow. So, as we give dead time in voltage-fed converters, here we have to give overlap time. However, I am facing a lot of doubts and problems. Some of them are:

1. How will I use de-sat protection?

2. How will I ensure other protection schemes such as over voltage?

3. How will I ensure that there is always some path for conduction and current never gets chopped?

I would be highly obliged if one can suggest me a good IC.

Edit: Also How will it help if I use MOSFET instead of IGBTs as no Desat protection is used for MOSFET?

I am trying to find a gate driver for IGBTs for a current-source full bridge topology. The main difference between current-fed and normal voltage-fed converters is that due to a boost inductance at the input, there should always be a path of current flow. So, as we give dead time in voltage-fed converters, here we have to give overlap time. However, I am facing a lot of doubts and problems. Some of them are:

1. How will I use de-sat protection?

2. How will I ensure other protection schemes such as over voltage?

3. How will I ensure that there is always some path for conduction and current never gets chopped?

I would be highly obliged if one can suggest me a good IC.

Edit: Also How will it help if I use MOSFET instead of IGBTs as no Desat protection is used for MOSFET?

Last edited: