Hi

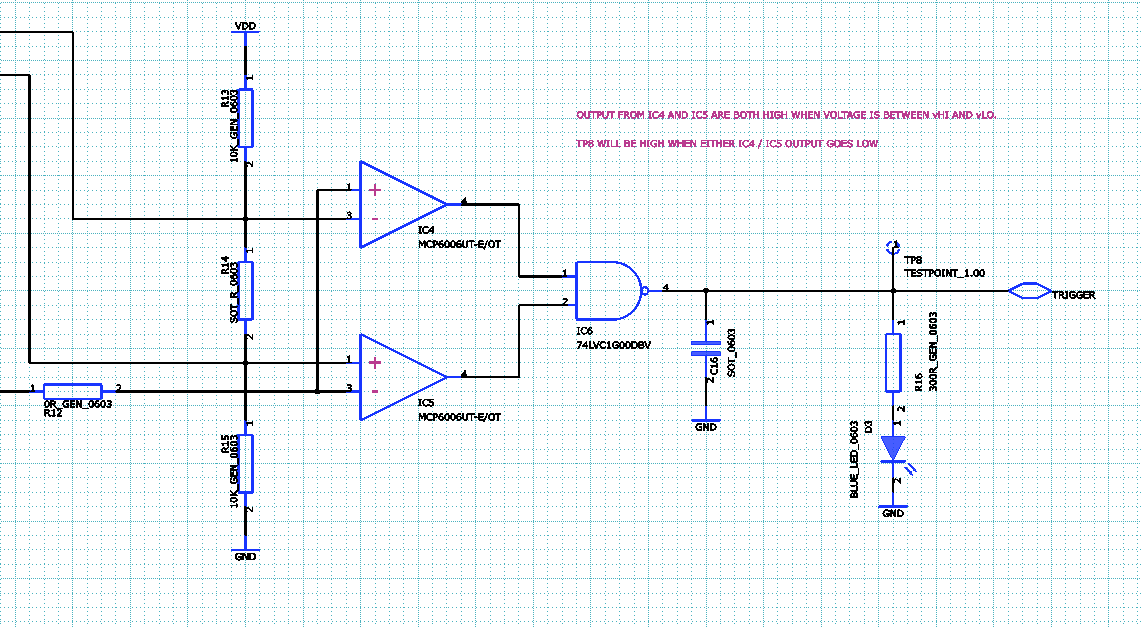

Below is a schematic of a window comparator.

I followed this schematic from one i found online.

As i understood it, when the input voltage was within the window, both outputs from IC4/IC5 would be high. Leaving the window on either side results in that opamp output going low.

In this circuit, i get the opposite behaviour. IC4/IC5 are output low, until leaving the window when one goes high.

This results in the NAND gate not being appropriate. An OR gate will be needed here instead.

My confusion is why, based on this schematic, do the outputs remain low while inside the window?

Thanks in advance for your help.

Below is a schematic of a window comparator.

I followed this schematic from one i found online.

As i understood it, when the input voltage was within the window, both outputs from IC4/IC5 would be high. Leaving the window on either side results in that opamp output going low.

In this circuit, i get the opposite behaviour. IC4/IC5 are output low, until leaving the window when one goes high.

This results in the NAND gate not being appropriate. An OR gate will be needed here instead.

My confusion is why, based on this schematic, do the outputs remain low while inside the window?

Thanks in advance for your help.