Hi,

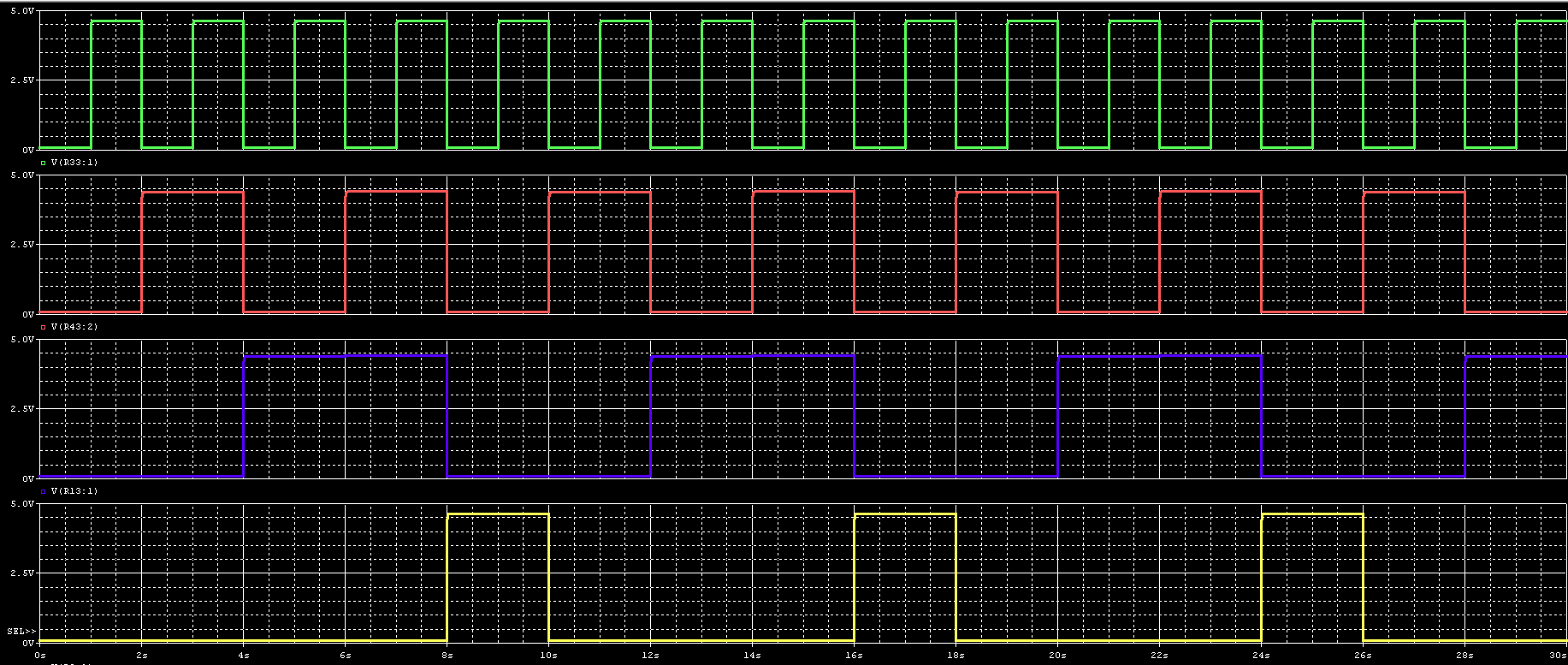

can you add the waveform at the emitter of Q19 to the simulation, so the reset logic timing is visible to check that?

A couple of practical problems, which I don't know if the sim will show or not:

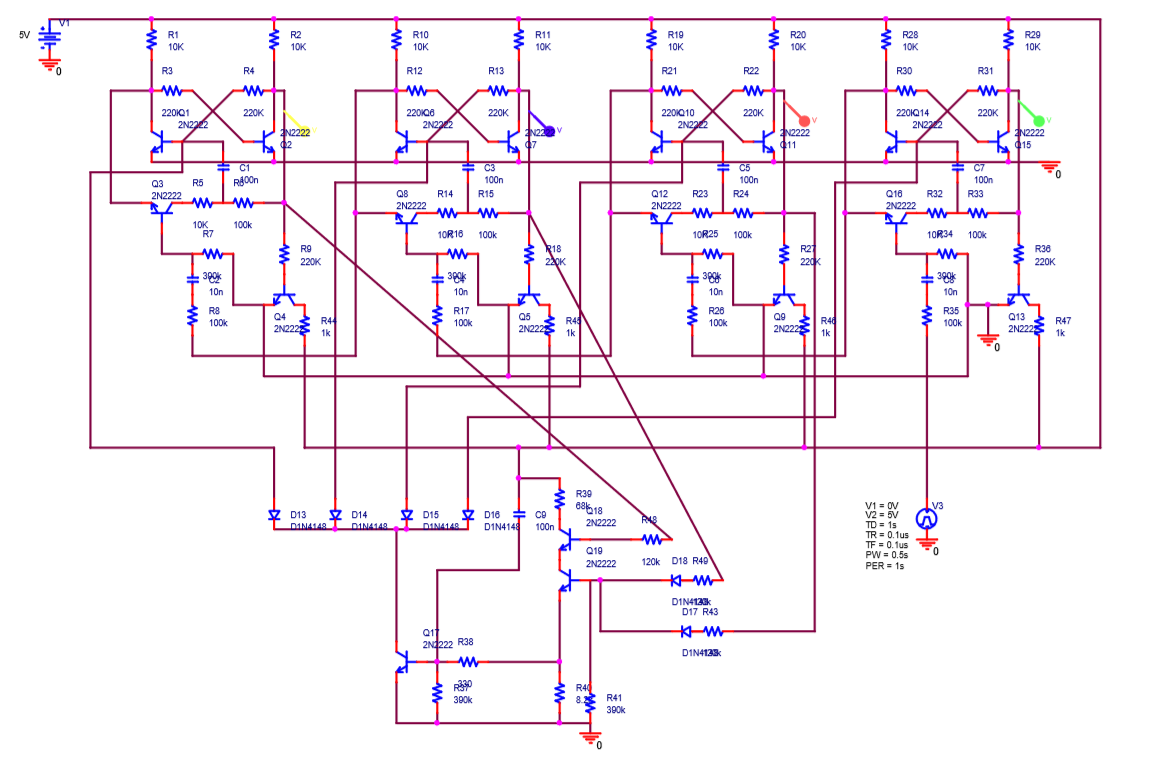

The diodes D13 - D16 in the reset circuit will have basically the same voltage drop as the base-emitter junctions of the transistors.

Add the collector voltage of Q17 when that is on and it's dubious whether any reset can happen as the transistors in the bistables may never switch off from Q17.

Possibly connect an extra diode in series with each bistable transistor base, so the input threshold becomes 1.2V? That should guarantee the reset circuit can remove the base drive. Add a high value resistor from base-emitter on each bistable transistor as well, so it definitely turns off with no current through the diode.

You _may_ get away with changing the reset diodes to schottky types, as they have a lower voltage drop.

And, "race conditions" - there is nothing to guarantee a finite duration of the reset pulse, so some bistables may reset (and remove the reset signal) before others respond.

Possibly add a small capacitor from the emitter of Q19 to ground, so Q17 is held on for a definite time after the reset logic gating no longer detects the reset count.

Nice circuit, by the way!

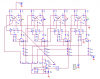

For info, this is a bit of commercial diode-transistor logic, a schematic of a logic board from a 1960s DEC PDP-8 minicomputer: