askingNo123

New Member

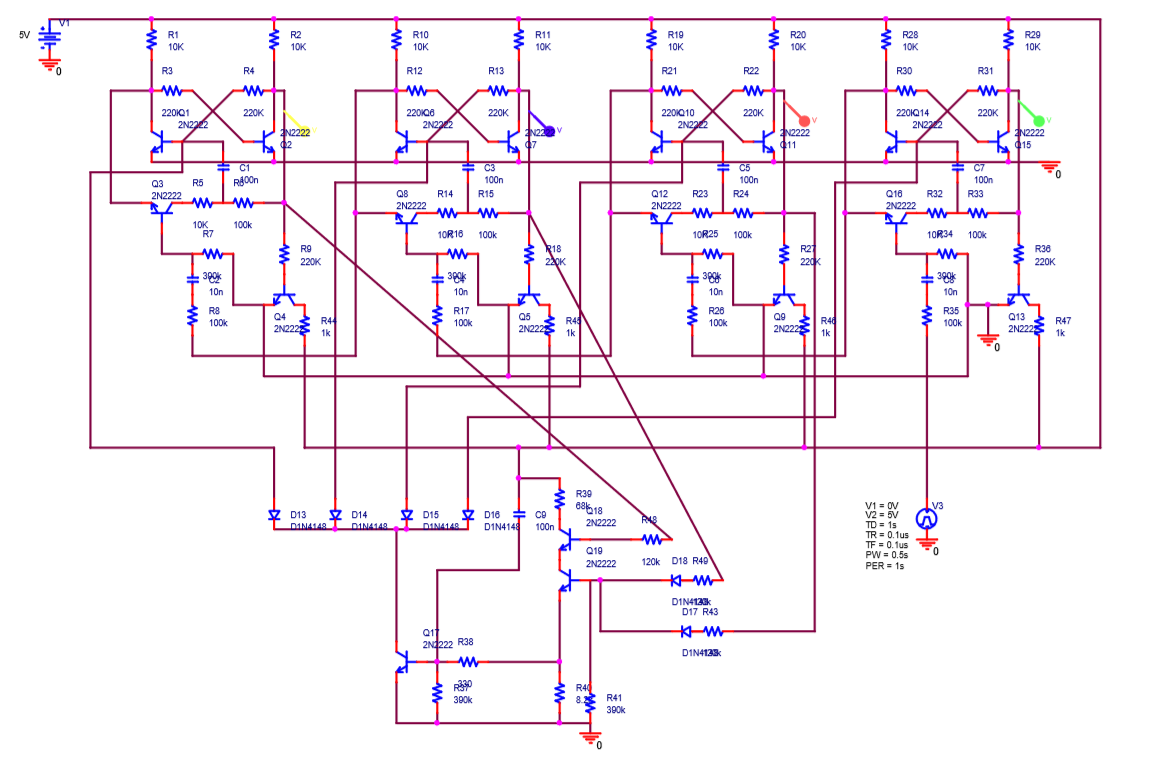

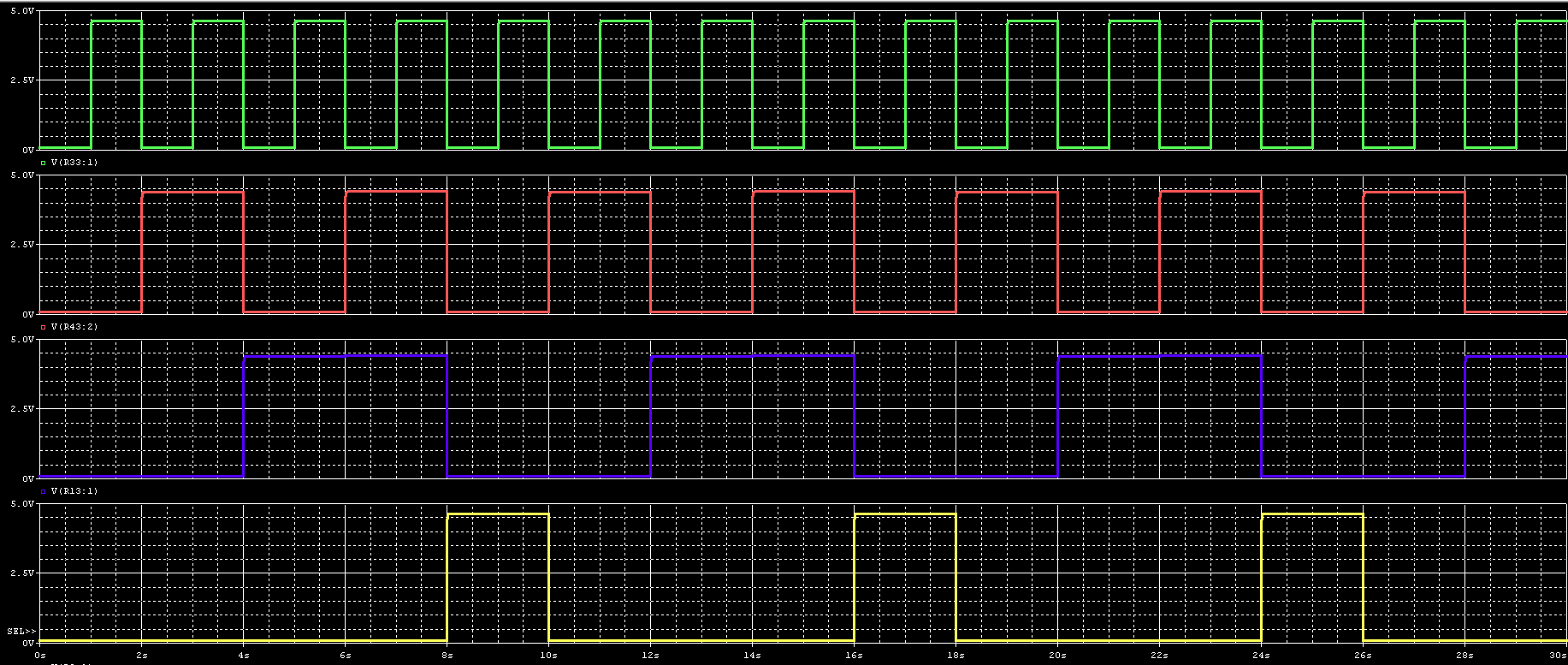

Hello, i'm new in electronic and i plan to make discrete bcd counter with T flip flop. Before i make it in real, i tried to make it in pspice. But when i pspice it, i found that second flip flop (which count as 2) does not reset when it is 10s (When it counts 1010) and because of it, reset occurs every 8 seconds after first reset. i can't find why it happens and how to solve it. Thanks you for your help.

Last edited: