Shadow_warrior

Member

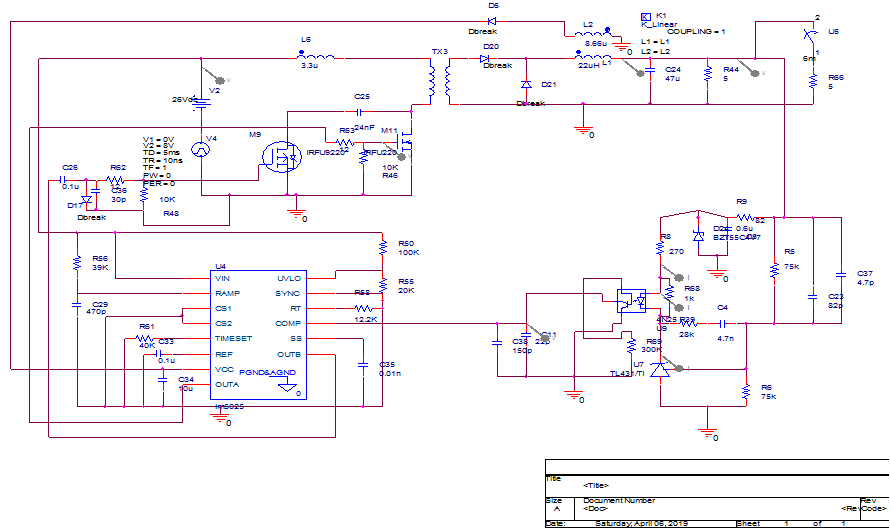

I am working on an Active Clamp Forward converter. Schematic is given here:

Specs:

It is working fine in open loop, but in closed loop I am getting a ripple in output Voltage of 2.5Volts Peak to peak.

Voltage waveform is given below:

I have designed controller considering settling time and load disturbance rejection. Here is the bode plot of my plant Gvd(s) and my plant+Controller.

What should I do to reduce the ripple in output voltage.

Note1: to implement the controller TL431 and opto-coupler 4N25 are used.

Note2: No ripple is seen in the simulation.

Thanks in advance.

Specs:

- Output voltage-5V

- Input voltage 26..42V

- frequency=500KHz

- Output power=10W

It is working fine in open loop, but in closed loop I am getting a ripple in output Voltage of 2.5Volts Peak to peak.

Voltage waveform is given below:

I have designed controller considering settling time and load disturbance rejection. Here is the bode plot of my plant Gvd(s) and my plant+Controller.

What should I do to reduce the ripple in output voltage.

Note1: to implement the controller TL431 and opto-coupler 4N25 are used.

Note2: No ripple is seen in the simulation.

Thanks in advance.