MacIntoshCZ

Active Member

Hello,

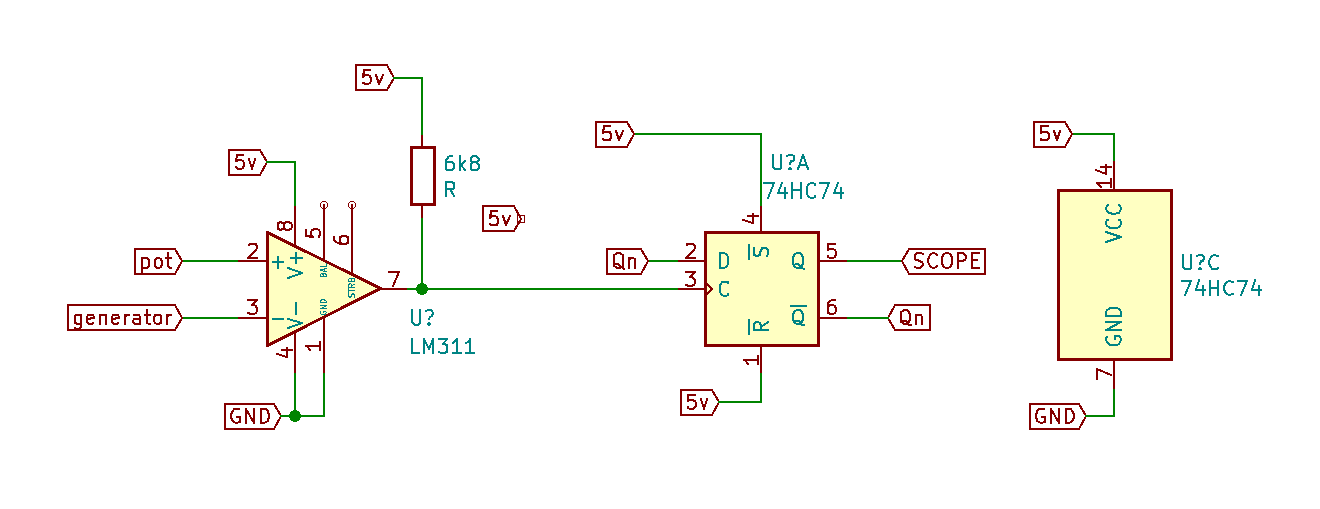

I am having trouble with my design. Its not working. LM311 is switching fine but i got just tiny pulse as response at Q 74hc74 output. When i apply signal (square wave) directly to flip flop it changes state. Using FY6900 as signal generator.

Do i missed something? LM311 Low logic VOLT is 0,25V , LO on 74hc74 is higher (up 1-2V i guess).

I am having trouble with my design. Its not working. LM311 is switching fine but i got just tiny pulse as response at Q 74hc74 output. When i apply signal (square wave) directly to flip flop it changes state. Using FY6900 as signal generator.

Do i missed something? LM311 Low logic VOLT is 0,25V , LO on 74hc74 is higher (up 1-2V i guess).