upand_at_them

Active Member

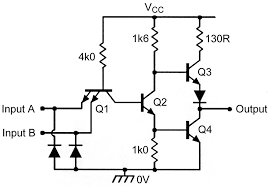

The image is a schematic of a 2-input NAND gate inside the SN7400. I'm confused how Q2 ever gets base current from the collector of Q1. My understanding is that when Q1 emitters are low, current flows from base to emitter...and since there's no voltage at the collector, no collector current flows. And when Q1 emitters are high, no base current flows...and there still is no collector current. I simulated this - with a one emitter NPN - on falstad.com and got the same results.

But clearly it must work. When Q1 emitters are high, Q2 base current must flow and turn on the transistor (which then turns off Q3 and turns on Q4). But how does Q2 get any base current?

But clearly it must work. When Q1 emitters are high, Q2 base current must flow and turn on the transistor (which then turns off Q3 and turns on Q4). But how does Q2 get any base current?