PG1995

Active Member

Thank you.

I'm trying to write a code for D flip-flop but I'm getting one error. Could you please help me with it? I understand that there would be many other easier ways to do this code but I'm trying to write my own code as much as possible.

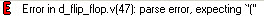

Error:

I'm trying to write a code for D flip-flop but I'm getting one error. Could you please help me with it? I understand that there would be many other easier ways to do this code but I'm trying to write my own code as much as possible.

Error:

C:

// Clock

module clock_10();

integer clk;

always begin

clk = 0;

#10 clk = 1;

#10;

end

endmodule

//D Flip-Flop

module D_flip_flop(Q_out,D_data,clk);

input clk;

input D_data;

output Q_out;

reg Q_out;

always @(posedge clk) begin

Q_out <= D_data;

end

endmodule

// Stimulus

module testbench;

reg D_data;

reg clk;

wire Q_out;

D_flip_flop d_flip_flop(Q_out,D_data,clk);

clock_10 clk; //line #47

initial

begin

D_data <= 1;

#25 D_data <= 0;

#45 D_data <= 1;

#65 D_data <= 0;

#50 $finish;

end

endmoduleAttachments

Last edited: