PG1995

Active Member

Thanks a lot.

I understand your point but for the time being I will stick to the way I have already written it assuming it's doesn't cause any compilation error.

Yes, you are right. I also think that using include directive isn't necessary as long as the other file is included in the project.

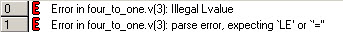

I'm getting the following errors for the code at the bottom. Please help me with it.

By the way, the file "two_to_1_mux" contains the code shown in post #13 above but I have omitted the "stimulus" part of code which is used for simulation. Thank you.

It is better to use the explicit connections like .Y(Y1) because late when you change something in your code and mess up the order it will keep working and not break up, just because the order of the parameters changed.

I understand your point but for the time being I will stick to the way I have already written it assuming it's doesn't cause any compilation error.

Yes, you are right. I also think that using include directive isn't necessary as long as the other file is included in the project.

I'm getting the following errors for the code at the bottom. Please help me with it.

Code:

two_to_1_mux mux1(Y1,A,B,Sel0,En);

two_to_1_mux mux2(Y2,C,D,Sel0,En);

two_to_1_mux mux3(Y3,Y1,Y2,Sel1,En);By the way, the file "two_to_1_mux" contains the code shown in post #13 above but I have omitted the "stimulus" part of code which is used for simulation. Thank you.

Attachments

Last edited: