Hi,

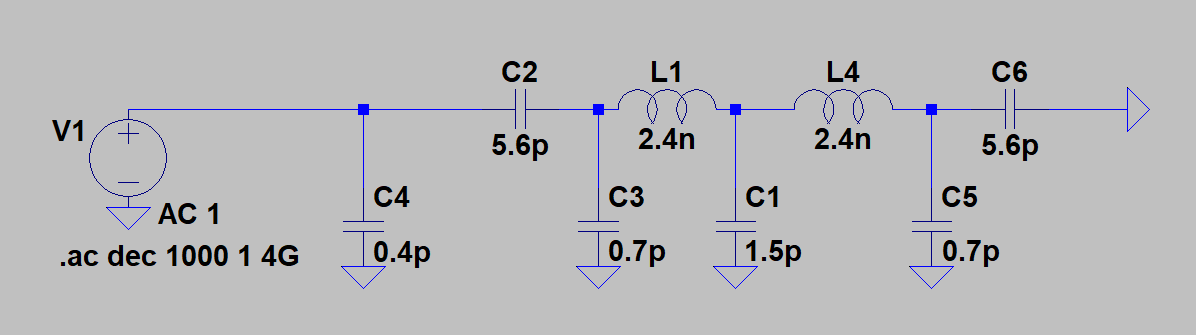

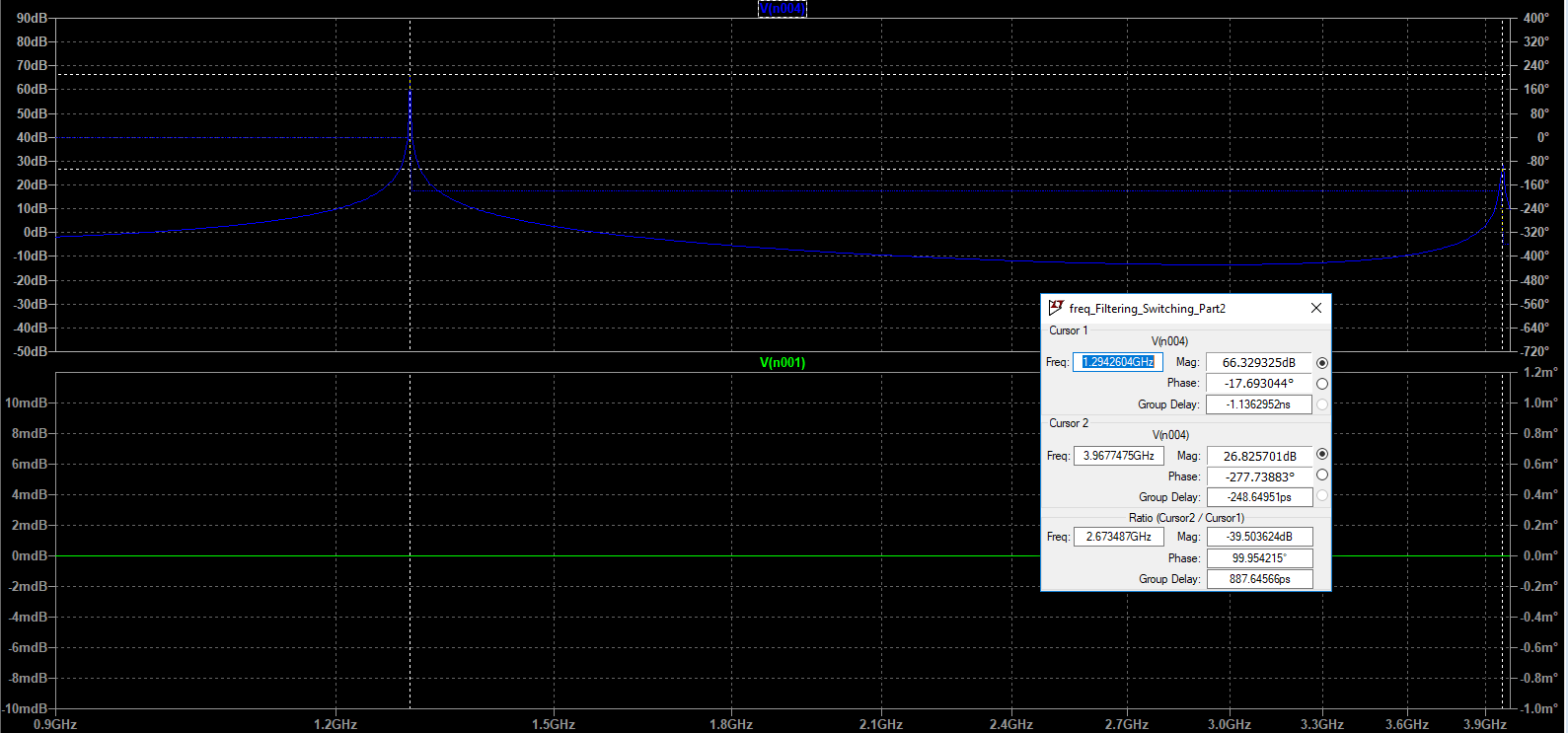

As attached, I did a simulation on LTspice running from 1MHz to 4 GHz. I ran it through a filter and was expected to see if the circuitry allowed me to attain the best reading of my values at 3.2GHz. Is it possible to say then that the peaks, corresponding to the resonant frequency attained form the circuit, are a result of a bandpass filter and that this means that the value attained shows that the circuit is not optimised for said frequency?

If not, how would i interpret these results.

(background info, these (1 of many)

are outputs from a synthesizer board)

are outputs from a synthesizer board)

Thank you in advance!

additionally i realised i may have used the wrong terminology, not resonant but cut-off freq!

As attached, I did a simulation on LTspice running from 1MHz to 4 GHz. I ran it through a filter and was expected to see if the circuitry allowed me to attain the best reading of my values at 3.2GHz. Is it possible to say then that the peaks, corresponding to the resonant frequency attained form the circuit, are a result of a bandpass filter and that this means that the value attained shows that the circuit is not optimised for said frequency?

If not, how would i interpret these results.

(background info, these (1 of many)

Thank you in advance!

additionally i realised i may have used the wrong terminology, not resonant but cut-off freq!

Last edited: