ADWSystems

Member

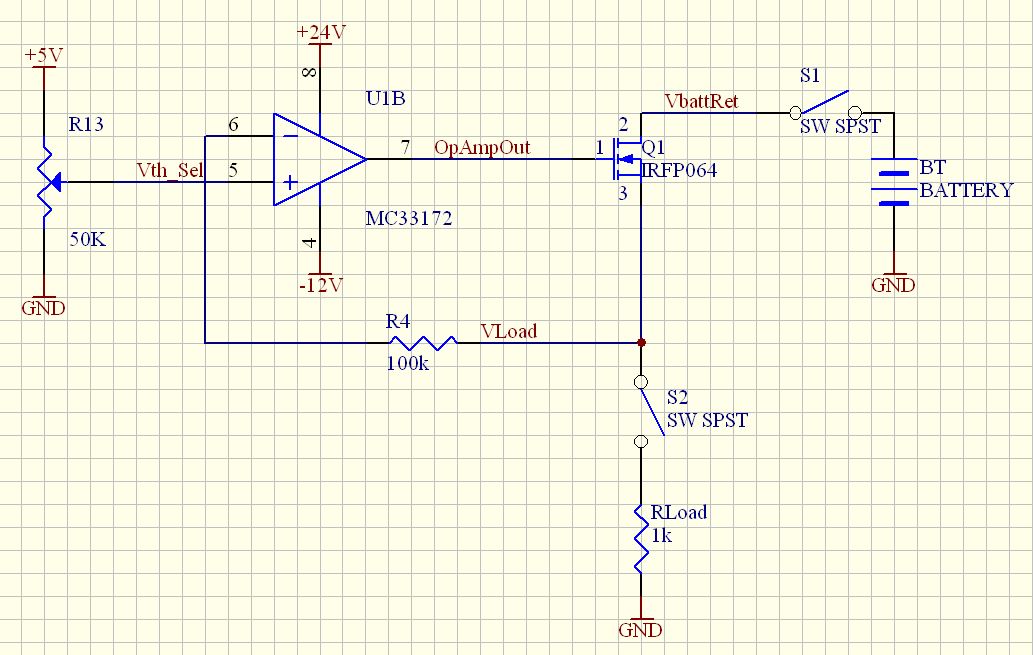

This is a continuation, hopefully the finalization of a long standing project.

It doesn't appear to be working as expected. I suspect a wiring issue but it could be design. We talked on this in the past and I have simulations, so I don't think its design. It could be the FET, it's been a while since I have worked with discrete FETs.

I have attached to AA batteries, not new so they only read 2.1V total.

When I closed S1 and S2, VbattRet and Vload go to 0.

I have some data points. but what I'm having trouble with is why when S2 is closed, does VbattRet and Vload go to 0?

With S1 open, and S2 open, Vth=1.6V, OpampOut is -12 , VbattRet is 1.67, Vload is 0.93

With S1 closed, and S2 open, Vth=1.6V, OpampOut is -12 , VbattRet is 1.75, Vload is 1.67

With S1 closed, and S2 closed, Vth=1.6V, OpampOut is 24 , VbattRet is 0, Vload is 0

With S1 open, and S2 open, Vth=3V, OpampOut is -12 , VbattRet is 0.93, Vload is 0.93

With S1 closed, and S2 open, Vth=3V, OpampOut is 24 , VbattRet is 1.77, Vload is 1.77

With S1 closed, and S2 closed, Vth=3V, OpampOut is 24 , VbattRet is 0, Vload is 0

Since Rload is between the battery + and ground, and I'm measuring across Rload, I would expect to see a positive voltage. But I read 0. It's acting like a short, but I can't seem to find it. The power supply voltages are stable and correct when VbattRet=0.

Were have I gone wrong with the circuit?

It doesn't appear to be working as expected. I suspect a wiring issue but it could be design. We talked on this in the past and I have simulations, so I don't think its design. It could be the FET, it's been a while since I have worked with discrete FETs.

I have attached to AA batteries, not new so they only read 2.1V total.

When I closed S1 and S2, VbattRet and Vload go to 0.

I have some data points. but what I'm having trouble with is why when S2 is closed, does VbattRet and Vload go to 0?

With S1 open, and S2 open, Vth=1.6V, OpampOut is -12 , VbattRet is 1.67, Vload is 0.93

With S1 closed, and S2 open, Vth=1.6V, OpampOut is -12 , VbattRet is 1.75, Vload is 1.67

With S1 closed, and S2 closed, Vth=1.6V, OpampOut is 24 , VbattRet is 0, Vload is 0

With S1 open, and S2 open, Vth=3V, OpampOut is -12 , VbattRet is 0.93, Vload is 0.93

With S1 closed, and S2 open, Vth=3V, OpampOut is 24 , VbattRet is 1.77, Vload is 1.77

With S1 closed, and S2 closed, Vth=3V, OpampOut is 24 , VbattRet is 0, Vload is 0

Since Rload is between the battery + and ground, and I'm measuring across Rload, I would expect to see a positive voltage. But I read 0. It's acting like a short, but I can't seem to find it. The power supply voltages are stable and correct when VbattRet=0.

Were have I gone wrong with the circuit?

Last edited: