PG1995

Active Member

Hi,

Could you please help me with this query? Thanks for the help!

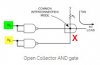

I understand that when two or more open-collector gates are combined, you get a wired-AND gate. But such a wired-AND gates has negative logic which means it gives HIGH output only when all its inputs are LOW. I agree with the expression on the right which says X=A'B'C'D' where A' means complement of A.

I do not understand why the author is using uncomplemented inputs to derive output expression in subsequent sections. Please see the green highlights where it is said that X=ABCDEFGH and X=ABCDEF.

Is there a mistake in the text, or is it just me? Please guide me.

Could you please help me with this query? Thanks for the help!

I understand that when two or more open-collector gates are combined, you get a wired-AND gate. But such a wired-AND gates has negative logic which means it gives HIGH output only when all its inputs are LOW. I agree with the expression on the right which says X=A'B'C'D' where A' means complement of A.

I do not understand why the author is using uncomplemented inputs to derive output expression in subsequent sections. Please see the green highlights where it is said that X=ABCDEFGH and X=ABCDEF.

Is there a mistake in the text, or is it just me? Please guide me.