Fluffyboii

Active Member

Hi, fist of all I want to say that I am unable to understand how BJTs operate. It seems simple, I calculate the values but when I try to simulate it on LTSpice or test it in real life things start to not make sense. When we started using Op Amps in class I was overjoyed because those thing act as they should in calculations because they are designed for it. But now they want us to make a multistage BJT amplifier with almost no information and just the requirements.

The hardest part seems to be achieving input impedance over 1M ohms. Also when I look at 2n2222 datasheet it says the Beta value is 35 but when I put one of those in my transistor tester I see values over 400. BC547 or similar BJTs show again higher than 300 Hfe values which makes no sense.

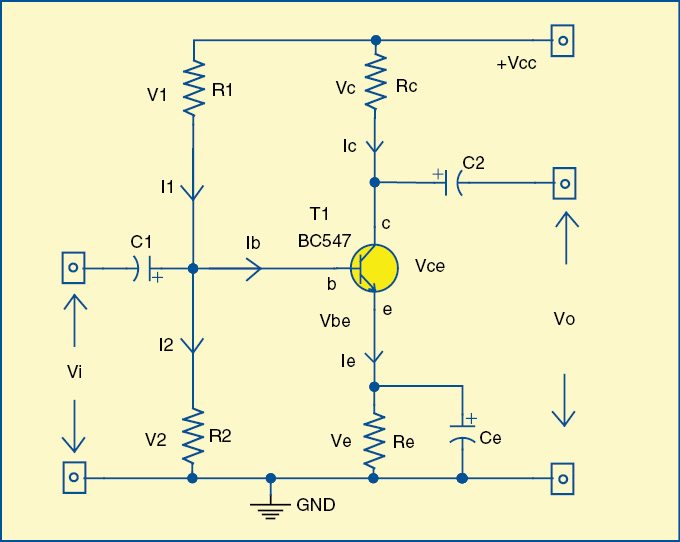

Anyway for my first test I decided to use a common emitter setup with high Re value to get a high input resistance. From my book it says the input resistance of a BJT CE amplifier is (B+1) (re +Re) so if I pick Re something like 3K ohms I should have over 1.2M ohm input resistance which is what I exactly did. The general rule of thumb seems to have %10 of voltage supply as voltage drop on Re so I picked 1.5V (15V supply) +0.7V should give me 2.2V Vb. Set the bias with a voltage divider. For my Ic value I picked 0.5mA and that gave me 15K ohm Rc resistance for 7.5V voltage drop on Rc. At the end I should have around -15K/3K = -5 times gain right? I assumed Ic and Ie as same since BJT has over 400 Beta.

Ok this was correct. I was having a delusional nightmare when I saw 8V and assumed 800 times gain but when I remember 7.5V center and saw 8V max and 7V bottom voltages I realised it was correct. Sometimes ranting about how stupid something makes me realise how stupid I am.

What can I do to have less than 100 ohms output resistance. I obviously need to increase the gain first. Logical thing to do seems to add a 20 times gain CE amplifier series with the first one to get non inverting 100 times gain then buffer it with another BJT to decrease the output impedance. But adding transistors in series causes them to affect each other and I am not sure how to pick the values for the second stage without distorting the signal. And how do I design them to have 20 times gain. I start with Ic current than calculate the other values from there which makes it hard to get the wanted gain without trial and error. I am sure there is a easy way to manipulate the equations and find it but I am unable to think right now. Actually it looks like If I pick Rc and Re values low enough I may be able to get away with only 2 stages without additional buffering.

The hardest part seems to be achieving input impedance over 1M ohms. Also when I look at 2n2222 datasheet it says the Beta value is 35 but when I put one of those in my transistor tester I see values over 400. BC547 or similar BJTs show again higher than 300 Hfe values which makes no sense.

Anyway for my first test I decided to use a common emitter setup with high Re value to get a high input resistance. From my book it says the input resistance of a BJT CE amplifier is (B+1) (re +Re) so if I pick Re something like 3K ohms I should have over 1.2M ohm input resistance which is what I exactly did. The general rule of thumb seems to have %10 of voltage supply as voltage drop on Re so I picked 1.5V (15V supply) +0.7V should give me 2.2V Vb. Set the bias with a voltage divider. For my Ic value I picked 0.5mA and that gave me 15K ohm Rc resistance for 7.5V voltage drop on Rc. At the end I should have around -15K/3K = -5 times gain right? I assumed Ic and Ie as same since BJT has over 400 Beta.

Ok this was correct. I was having a delusional nightmare when I saw 8V and assumed 800 times gain but when I remember 7.5V center and saw 8V max and 7V bottom voltages I realised it was correct. Sometimes ranting about how stupid something makes me realise how stupid I am.

What can I do to have less than 100 ohms output resistance. I obviously need to increase the gain first. Logical thing to do seems to add a 20 times gain CE amplifier series with the first one to get non inverting 100 times gain then buffer it with another BJT to decrease the output impedance. But adding transistors in series causes them to affect each other and I am not sure how to pick the values for the second stage without distorting the signal. And how do I design them to have 20 times gain. I start with Ic current than calculate the other values from there which makes it hard to get the wanted gain without trial and error. I am sure there is a easy way to manipulate the equations and find it but I am unable to think right now. Actually it looks like If I pick Rc and Re values low enough I may be able to get away with only 2 stages without additional buffering.