Electronaut

Member

Hello,

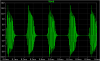

Here is a simple Hartley oscillator circuit in LTspice that when simulated results in a series of wave packets or "solitons."

The explanation seems clear: relaxation of capacitor C2 "modulates" the carrier frequency generated by the tank circuit formed by L1/L2/C1.

But when this circuit is realized on a breadboard the output is displayed on an oscilloscope, I get only the upper envelope. That is, the output is rectified.

Any ideas why this happens?

Thanks,

Electronaut

Here is a simple Hartley oscillator circuit in LTspice that when simulated results in a series of wave packets or "solitons."

The explanation seems clear: relaxation of capacitor C2 "modulates" the carrier frequency generated by the tank circuit formed by L1/L2/C1.

But when this circuit is realized on a breadboard the output is displayed on an oscilloscope, I get only the upper envelope. That is, the output is rectified.

Any ideas why this happens?

Thanks,

Electronaut