My preference is to add a FF to the counter reset to avoid any concerns about a race problem or having to add a kludge RC delay.

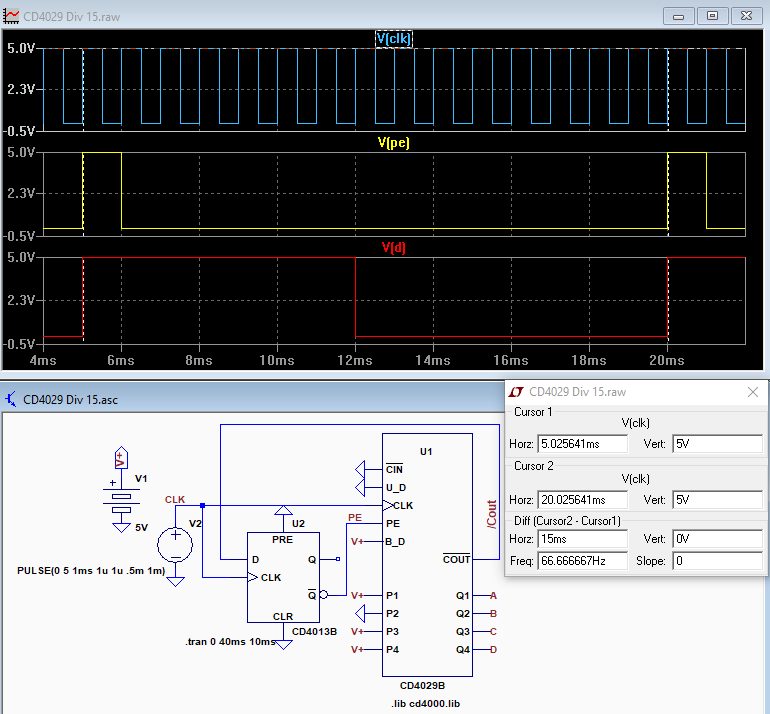

Below is a CD4029B up/dn counter with parallel-load, configured as a down-counter to do a divide by 15.

The FF gives a clean, one clock-period-wide reset (Parallel-load Enable) signal.

The total number of ICs is the same as using a counter with a decode gate.

Edit:

Below is a circuit that uses a 74HC163 synchronous parallel-load (up) counter so it needs just an inverter instead of a FF to give a full single-clock-period, Parallel-load Enable signal.

Below is a CD4029B up/dn counter with parallel-load, configured as a down-counter to do a divide by 15.

The FF gives a clean, one clock-period-wide reset (Parallel-load Enable) signal.

The total number of ICs is the same as using a counter with a decode gate.

Edit:

Below is a circuit that uses a 74HC163 synchronous parallel-load (up) counter so it needs just an inverter instead of a FF to give a full single-clock-period, Parallel-load Enable signal.

Last edited: