Hi,

I might be able to help a little here.

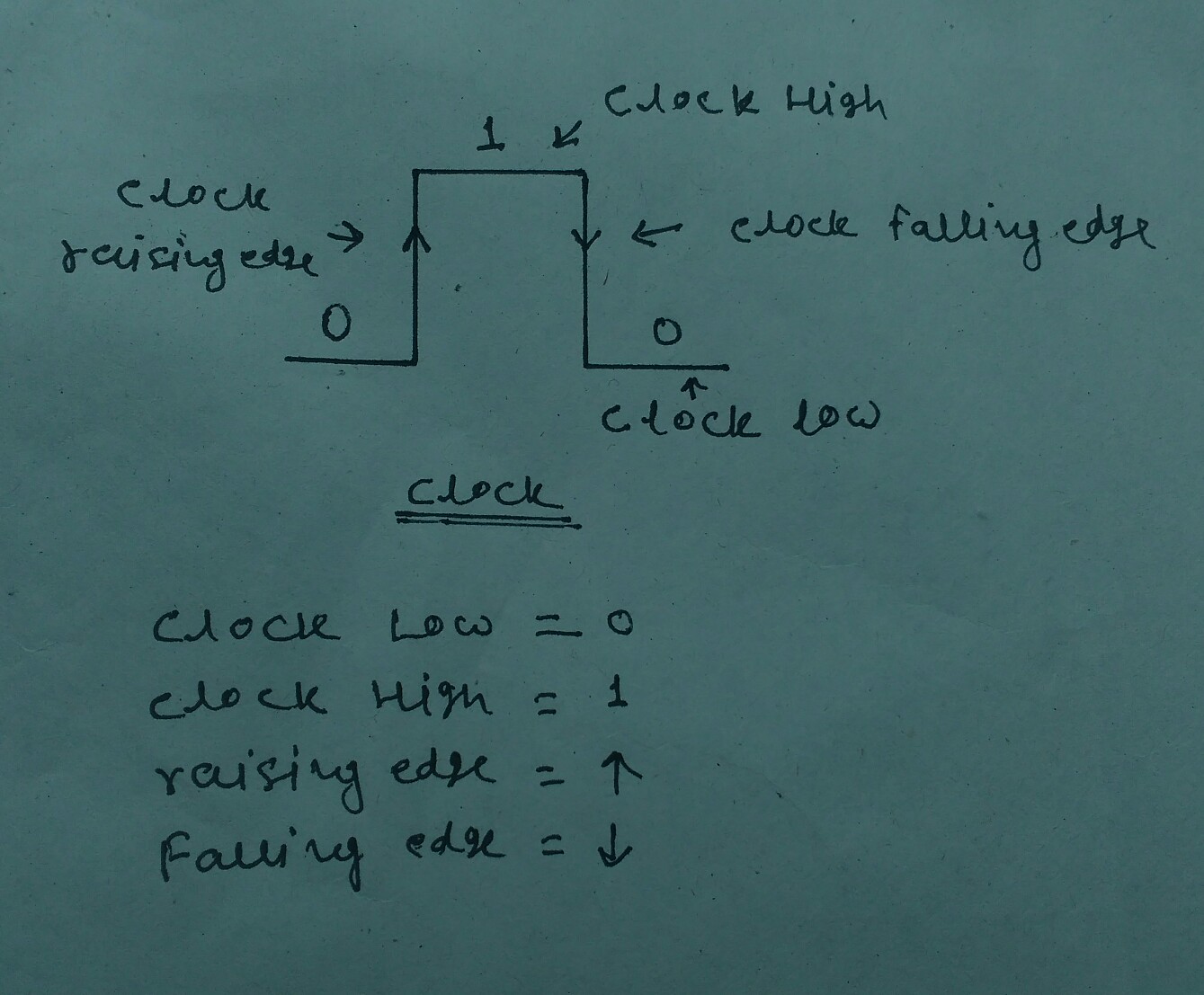

First the operation of a single D flip flop should be completely understood. Then, to understand how two work in tandem you only need to look at the two outputs at the same time to see what they are doing with each input clock pulse.

Starting with a single D-FF, when the D is high the Q clocks to a high and the Q' clocks to a low (Q'=notQ or Qnot).

Nothing else happens yet, just that, except of course that the D changes from a high to a low because the Q' went low now.

So look at it again and see that now the D is low.

The next clock (rising clock edge) makes the FF clock the Q into a low now because the D input is low. That also manes teh Q' high again, which makes the D input high again.

So see now we are right back where we started, with the D high and the Q low and the Q' high.

What could possibly happen next? Same thing. The process repeats, so with every clock edge the Q output changes state and so does the Q'. If you look at the frequency the Q output goes high with one clock and low with the next clock, so therefore it takes 2 clocks to get one cycle out of the Q, which means the Q frequency is 1/2 of the clock frequency.

Now we come to the second stage.

The second stage FF works exactly like the first, except it gets it's clock from the Q of the preceeding stage. That means it's output Q will only change once per output of the first FF, which means the frequency of that Q will be 1/2 of the first FF or 1/4 of the original input clock frequency.

If we look at the stages of each Q while this is happening, we'll see:

00

01

10

11

in binary on the two Q outputs. Thus we have a 2 bit counter.

The type of counter in this case is a binary ripple counter.