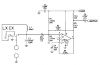

I've built this oscillator for determine the resonance of LC tanks:

https://www.qsl.net/iz7ath/web/02_brew/21_LCMeter01/fig/fig08.gif

except that I didn't implement the NAND gate buffer. Instead I'm trying to use just a 2n7000 N-FET (common source configuration with a 10K drain pull-up). The problem is that I'm seeing substantial glitches (~ .5 V) on the up transitions and the rise time is now very noticable. The high-to-low transitions are fine.

I'd like to square up the output signal as much as possible without using another CMOS IC. Any suggestions? Should I use a different transistor? smaller pull-up? add a cap somewhere?

For reference, here's the associated article for the schematic:

https://www.qsl.net/iz7ath/web/02_brew/21_LCMeter01/

https://www.qsl.net/iz7ath/web/02_brew/21_LCMeter01/fig/fig08.gif

except that I didn't implement the NAND gate buffer. Instead I'm trying to use just a 2n7000 N-FET (common source configuration with a 10K drain pull-up). The problem is that I'm seeing substantial glitches (~ .5 V) on the up transitions and the rise time is now very noticable. The high-to-low transitions are fine.

I'd like to square up the output signal as much as possible without using another CMOS IC. Any suggestions? Should I use a different transistor? smaller pull-up? add a cap somewhere?

For reference, here's the associated article for the schematic:

https://www.qsl.net/iz7ath/web/02_brew/21_LCMeter01/

Last edited: