Hi,

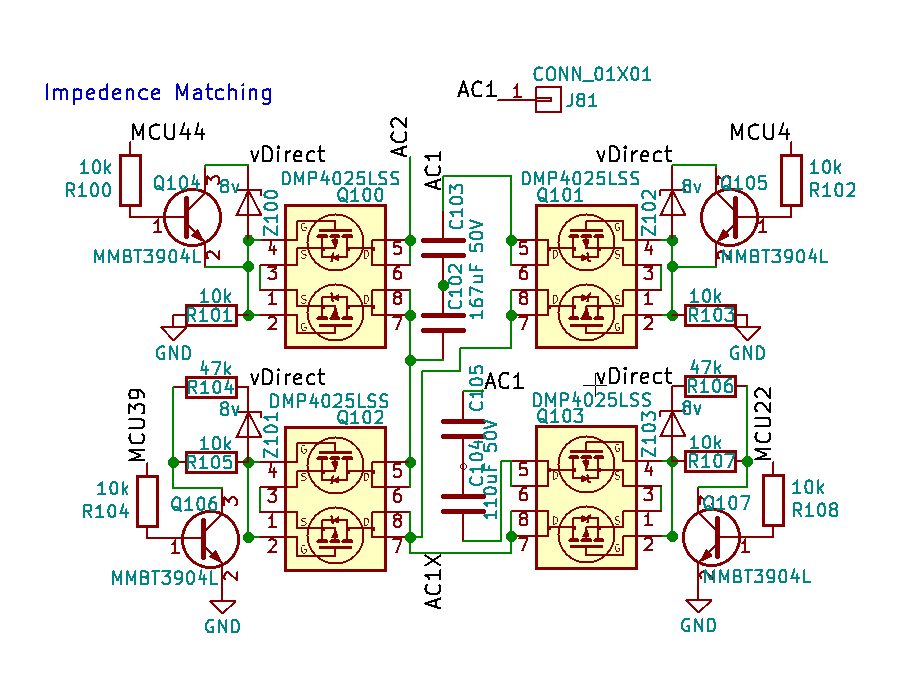

I just want to clarify this circuit looks reasonable without any potential snags.

AC1 and AC2 is 0-40V. AC1X and AC2 go to rectification, so the idea here is to place capacitance in series between AC1 and AC1X and/or in parallel between AC1 and AC2 (and short AC1 and AC1X together). These are;

110uF between AC1 and AC1X

167uF between AC1 and AC2, short AC1 & AC1X

167uF between AC1 and AC1X

FET's don't need to turn on quickly so no drivers required. I have a bit of a fetish for P-channel FET's, but it's because they're high side. The ensure circuit uses 34 P-fets and only 2 N-fets, which makes me wonder if there's anything better.

Vdirect is the rectified voltage. I'm using active rectification so technically the voltage should be nigh on identical to AC1/2, ensuring the FET turns off completely. The zeners prevent under-voltaging the gate. The transistors are because I'm cheap, but also they'll withstand 40V. Q104/5 will thus present a voltage drop but it should be low enough to ensure the FET is off.

Is there an easier way? Triacs would be nice if they didn't have a 0.7V voltage drop. Depleted FET's don't reduce the component count much and usually have reduced performance or higher cost. Any voltage drop is considered make-or-break - a relay is better than a 0.7V drop.

I have no electrical education or background, and I have no idea what I'm talking about.

Cheers!

Andrew

I just want to clarify this circuit looks reasonable without any potential snags.

AC1 and AC2 is 0-40V. AC1X and AC2 go to rectification, so the idea here is to place capacitance in series between AC1 and AC1X and/or in parallel between AC1 and AC2 (and short AC1 and AC1X together). These are;

110uF between AC1 and AC1X

167uF between AC1 and AC2, short AC1 & AC1X

167uF between AC1 and AC1X

FET's don't need to turn on quickly so no drivers required. I have a bit of a fetish for P-channel FET's, but it's because they're high side. The ensure circuit uses 34 P-fets and only 2 N-fets, which makes me wonder if there's anything better.

Vdirect is the rectified voltage. I'm using active rectification so technically the voltage should be nigh on identical to AC1/2, ensuring the FET turns off completely. The zeners prevent under-voltaging the gate. The transistors are because I'm cheap, but also they'll withstand 40V. Q104/5 will thus present a voltage drop but it should be low enough to ensure the FET is off.

Is there an easier way? Triacs would be nice if they didn't have a 0.7V voltage drop. Depleted FET's don't reduce the component count much and usually have reduced performance or higher cost. Any voltage drop is considered make-or-break - a relay is better than a 0.7V drop.

I have no electrical education or background, and I have no idea what I'm talking about.

Cheers!

Andrew