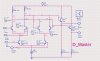

This component is from the ADS 2008 example, I don't quite understand how it works clearly.

By far I think that if D=0,CLK=1 , then the collector current Ic of BJT1 is small, resulting in that Vc of BJT1 is High, hence Vb of BJT14 is High and BJT14 is active, so [LATEX]\bar{Q}[/LATEX]=1.

But I have no idea how to figure out Q when D=0, CLK=1, can anyone give me a hint?

By far I think that if D=0,CLK=1 , then the collector current Ic of BJT1 is small, resulting in that Vc of BJT1 is High, hence Vb of BJT14 is High and BJT14 is active, so [LATEX]\bar{Q}[/LATEX]=1.

But I have no idea how to figure out Q when D=0, CLK=1, can anyone give me a hint?