Shadow_warrior

Member

Hello people!

I am working on Dual Active Bridge with following specifications:

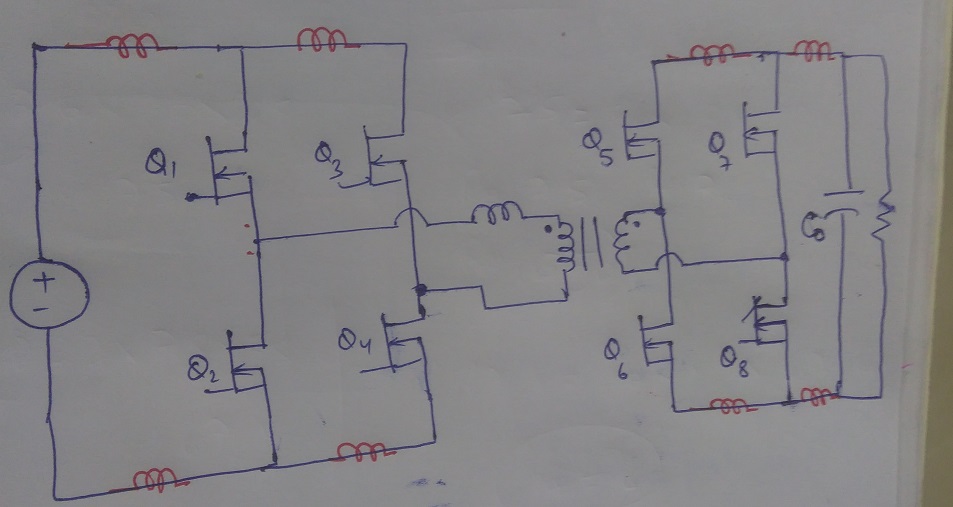

The inductance in blue is the discrete inductance I will add separately apart from that of leakage of transformer, However I want to eliminate the Inductances marked in red. Before starting the layout I wanted some tips from you guys. Also, I would be really obliged if someone can guide me to some reference materials.

One more thing I want to mention is that I have to make a generic layout which will also have provision of paralling of FETs. Like instead of Q1 I will add two FETs Q1a and Q1b and similarly for all switches.

I am working on Dual Active Bridge with following specifications:

- Frequency=50KHz

- Input Current 20A(rms)

- Input Voltage=60V

- Output Voltage 400V

- Output Power=1.2KW

The inductance in blue is the discrete inductance I will add separately apart from that of leakage of transformer, However I want to eliminate the Inductances marked in red. Before starting the layout I wanted some tips from you guys. Also, I would be really obliged if someone can guide me to some reference materials.

One more thing I want to mention is that I have to make a generic layout which will also have provision of paralling of FETs. Like instead of Q1 I will add two FETs Q1a and Q1b and similarly for all switches.