PG1995

Active Member

Hi,

Please have a look here. Could you please help me with the query?

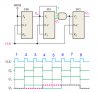

It is said that the AND gate has a fault and its lower input, i.e. #2 input, is always HIGH internally.

It means the output of AND gate is controlled by upper input, i.e. #1, and input comes from Q0.

When Q0 is HIGH, the output Q2 of rightmost flip flop, FF2 (EDIT: it was written FF3 previously), toggles. When Q0 is LOW, FF3 gets RESET. But this is not what happening when you look at the waveform. For example, at "X", Q0 is LOW but Q2 is still HIGH. Could you please help me?

Thank you!

Please have a look here. Could you please help me with the query?

It is said that the AND gate has a fault and its lower input, i.e. #2 input, is always HIGH internally.

It means the output of AND gate is controlled by upper input, i.e. #1, and input comes from Q0.

When Q0 is HIGH, the output Q2 of rightmost flip flop, FF2 (EDIT: it was written FF3 previously), toggles. When Q0 is LOW, FF3 gets RESET. But this is not what happening when you look at the waveform. For example, at "X", Q0 is LOW but Q2 is still HIGH. Could you please help me?

Thank you!

Attachments

Last edited: