To the Ineffable All,

I have some articles from old journals and texts that I have collected throughout the years. I consider this information "old gold". I am going to share one article called Remapping Technique Trades Gates for Flip-Flops. I think it came from Electronics World, May 15, 1971, but I am not sure of the publication name, which is missing from the copied article. The copy is faded and hard to read, but I constructed the knowledge as best as I can. It presents a technique called "parallel mapping", which I have never found in text books or elsewhere. If anyone knows of a reference to this topic, I would appreciate a link.

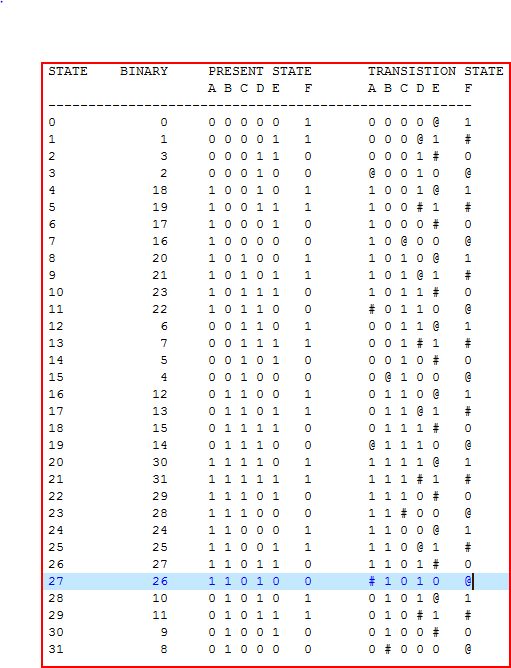

The article demonstrates a design of a 5-bit Gray code counter. As most of you know, a Gray code sequence changes only 1 bit at a time. This counter will have 32 states and 5 counting flip-flops (FF). Let's start by looking at the truth table for such a counter below.

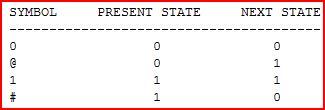

As you can see, the binary value of each state is also listed, which makes it easy to plot each flip-flop in the transistion table into a Karnaugh map (K-map). The highest logic value is FF "A" and the lowest is FF "E". Ignore FF "F" for the moment. The transistion table shows the change from the present state to the next state according to the table below. Thus by plotting the transistions of each FF, we can determine what the inputs should be to make each FF output a particular logic sequence.

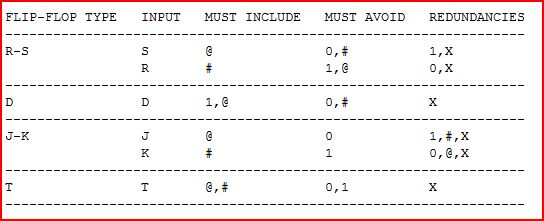

Once we plot the transistion table into a K-map, we can determine the best FF to use. This is determined by the FF characteristic table below.

The K-maps of the transistions of all the variables are shown in the included attachments. Ignore the orange marking for the moment. It will be explained later. A FF type is selected by observing the fewest gates needed at the FF input. I assume that everyone reading this post knows how to use a K-map. The selections made according to the inputs needed for each gate are as follows:

FF-A---> D type

FF-B---> JK type

FF-C---> JK type

FF-D---> D type

FF-E---> D type

Connecting all the leads according to the minimized terms, we get the counter shown in the attachment Normal Gray Code.pdf.

Now comes the interesting part. As I said before, I have never come across this technique called parallel mapping anywhere else. First a word about the D-type FF. Any input into a D type FF will output the same input one clock cycle later. Look at FF-F in the PRESENT STATE table above. If we pipe the output of the F-FF to the input of the E-FF, we will get the desired output from the E-FF. The transistion table for the F-FF shows we should input a E' from the E-FF to make the output of the F-FF come out correctly. We can also use the positive and negative output of the F-FF as input to the other FF's to eliminate a lot of gates. You can see this parallel mapping on the K-maps by observing the orange FF-F overlay. Using the output from the F-FF we get:

FF-A---> J = K = DE'F'

FF-B---> J = K = A'D'E'F'

FF-C---> J = K = AD'E'F'

DD-D---> J = K = EF

FF-E---> F

The reduction of gates can be seen by looking at the attachment Reduced Gray Code.pdf. By substituting one gate for several FF's, the component count is reduced. Both circuits output a Gray code sequence, but there is a big difference in the number of gates used. An even greater reduction in component count can be had if AND JK FF's like the MC3050 are used. Then no separate gates are needed. Both circuits were tested on VisualSpice and work as expected.

Ratch

I have some articles from old journals and texts that I have collected throughout the years. I consider this information "old gold". I am going to share one article called Remapping Technique Trades Gates for Flip-Flops. I think it came from Electronics World, May 15, 1971, but I am not sure of the publication name, which is missing from the copied article. The copy is faded and hard to read, but I constructed the knowledge as best as I can. It presents a technique called "parallel mapping", which I have never found in text books or elsewhere. If anyone knows of a reference to this topic, I would appreciate a link.

The article demonstrates a design of a 5-bit Gray code counter. As most of you know, a Gray code sequence changes only 1 bit at a time. This counter will have 32 states and 5 counting flip-flops (FF). Let's start by looking at the truth table for such a counter below.

As you can see, the binary value of each state is also listed, which makes it easy to plot each flip-flop in the transistion table into a Karnaugh map (K-map). The highest logic value is FF "A" and the lowest is FF "E". Ignore FF "F" for the moment. The transistion table shows the change from the present state to the next state according to the table below. Thus by plotting the transistions of each FF, we can determine what the inputs should be to make each FF output a particular logic sequence.

Once we plot the transistion table into a K-map, we can determine the best FF to use. This is determined by the FF characteristic table below.

The K-maps of the transistions of all the variables are shown in the included attachments. Ignore the orange marking for the moment. It will be explained later. A FF type is selected by observing the fewest gates needed at the FF input. I assume that everyone reading this post knows how to use a K-map. The selections made according to the inputs needed for each gate are as follows:

FF-A---> D type

FF-B---> JK type

FF-C---> JK type

FF-D---> D type

FF-E---> D type

Connecting all the leads according to the minimized terms, we get the counter shown in the attachment Normal Gray Code.pdf.

Now comes the interesting part. As I said before, I have never come across this technique called parallel mapping anywhere else. First a word about the D-type FF. Any input into a D type FF will output the same input one clock cycle later. Look at FF-F in the PRESENT STATE table above. If we pipe the output of the F-FF to the input of the E-FF, we will get the desired output from the E-FF. The transistion table for the F-FF shows we should input a E' from the E-FF to make the output of the F-FF come out correctly. We can also use the positive and negative output of the F-FF as input to the other FF's to eliminate a lot of gates. You can see this parallel mapping on the K-maps by observing the orange FF-F overlay. Using the output from the F-FF we get:

FF-A---> J = K = DE'F'

FF-B---> J = K = A'D'E'F'

FF-C---> J = K = AD'E'F'

DD-D---> J = K = EF

FF-E---> F

The reduction of gates can be seen by looking at the attachment Reduced Gray Code.pdf. By substituting one gate for several FF's, the component count is reduced. Both circuits output a Gray code sequence, but there is a big difference in the number of gates used. An even greater reduction in component count can be had if AND JK FF's like the MC3050 are used. Then no separate gates are needed. Both circuits were tested on VisualSpice and work as expected.

Ratch