MacIntoshCZ

Active Member

Hello there after a while =),

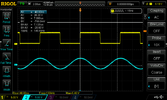

Blue trace is from DDS generator, its should simulate feedback from current transformer - tag: CT

Yellow trace is output from VCO.

I though phases will be same. Howeever current in coil is shifted by 90 degrees so i should no complain about that... I will use this for driving halfbridge.

Can someone explain why its shifted?

Thanks

Blue trace is from DDS generator, its should simulate feedback from current transformer - tag: CT

Yellow trace is output from VCO.

I though phases will be same. Howeever current in coil is shifted by 90 degrees so i should no complain about that... I will use this for driving halfbridge.

Can someone explain why its shifted?

Thanks