Hi,

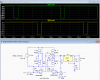

For the attached schematic I need to limit the gate voltages for the N/P Fets. For the N this is simple however for the P gates the voltage swings to ground via the comparator. Assuming a Vcc of 20V created by a resistor/zener between Vout and GND, what's the correct method to ensure the comparator swings between Vout and Vcc?

For the attached schematic I need to limit the gate voltages for the N/P Fets. For the N this is simple however for the P gates the voltage swings to ground via the comparator. Assuming a Vcc of 20V created by a resistor/zener between Vout and GND, what's the correct method to ensure the comparator swings between Vout and Vcc?