PG1995

Active Member

Hi,

Please have a look on this attachment.

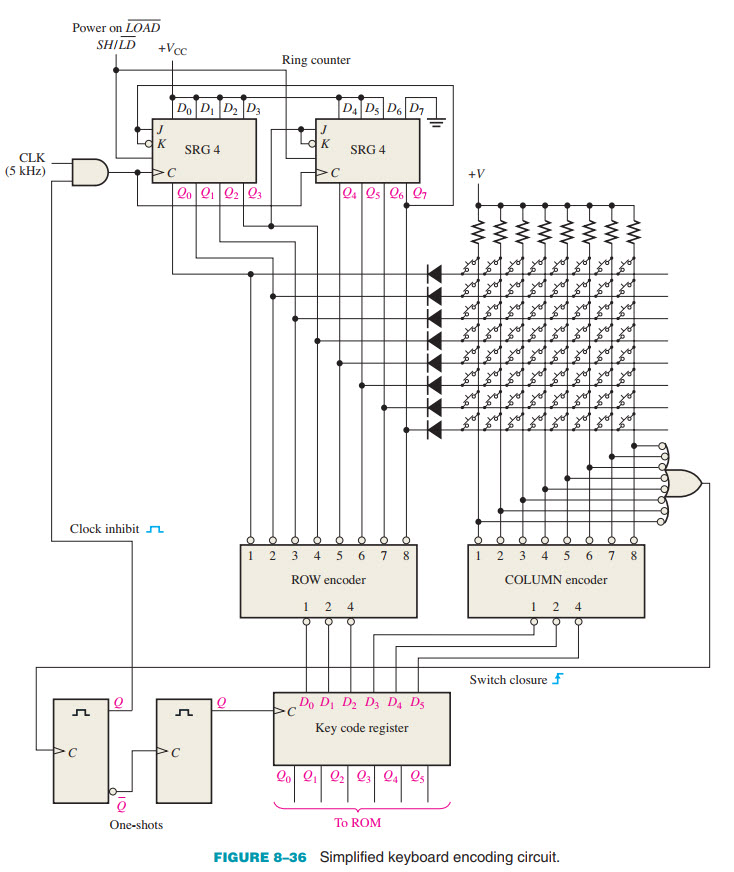

It says, "When a key is closed, the two one-shots produce a delayed clock pulse to parallel-load the 6-bit code into the key code register. This delay allows the contact bounce to die out. Also, the first one-shot output inhibits the ring counter to prevent it from scanning while the data are being loaded into the key code register."

The clock pulse is fed to both serial registers or ring counter through an AND gate. One input into the AND gate comes from a clock and the other comes from one-shot on the left. For the clock pulse to pass through AND gate, the input coming one-shot should normally be HIGH.

Question:

Is the one-shot on left produce HIGH-to-LOW pulse when triggered? What about the one-shot on right? Thank you for your help!

Please have a look on this attachment.

It says, "When a key is closed, the two one-shots produce a delayed clock pulse to parallel-load the 6-bit code into the key code register. This delay allows the contact bounce to die out. Also, the first one-shot output inhibits the ring counter to prevent it from scanning while the data are being loaded into the key code register."

The clock pulse is fed to both serial registers or ring counter through an AND gate. One input into the AND gate comes from a clock and the other comes from one-shot on the left. For the clock pulse to pass through AND gate, the input coming one-shot should normally be HIGH.

Question:

Is the one-shot on left produce HIGH-to-LOW pulse when triggered? What about the one-shot on right? Thank you for your help!