peterwarzeck

New Member

Hi Guys, i am stuck with this problem:

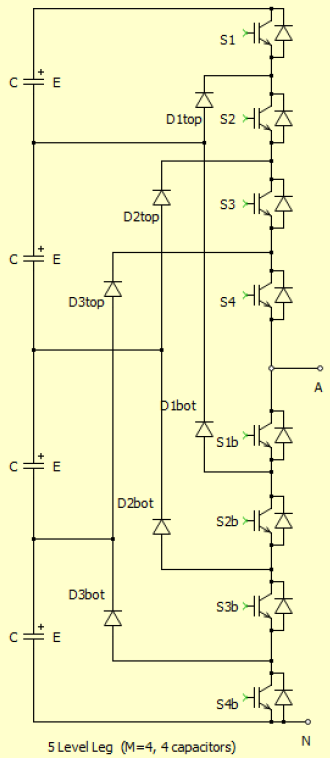

The image below shows a single Inverter Leg (phase a) of a Diode Clamped Multilevel Converter with M=4 capacitors.

If a three phase inverter has 3 such identical legs (as shown below) connected in Y with common node at N and line terminals (A,B,C), what is the maximum RMS line voltage possible in terms of E.

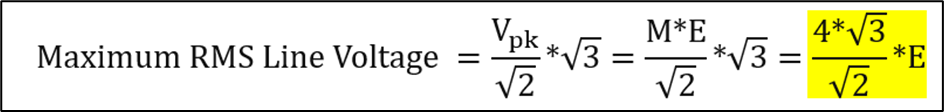

Based on my understanding, my answer is:

My reasoning:

The maximum attainable RMS phase voltage without distortion for one leg is given by M*E/sqrt(2), where M is the number of levels minus one and E is the voltage of one DC source. The relationship between the line voltage and phase voltage in a 'Y' configuration is to multiply the line voltage by sqrt(3). Hence i got my solution.

Please let me know if my method is correct or correct me if i am wrong. Thank you

The image below shows a single Inverter Leg (phase a) of a Diode Clamped Multilevel Converter with M=4 capacitors.

If a three phase inverter has 3 such identical legs (as shown below) connected in Y with common node at N and line terminals (A,B,C), what is the maximum RMS line voltage possible in terms of E.

Based on my understanding, my answer is:

My reasoning:

The maximum attainable RMS phase voltage without distortion for one leg is given by M*E/sqrt(2), where M is the number of levels minus one and E is the voltage of one DC source. The relationship between the line voltage and phase voltage in a 'Y' configuration is to multiply the line voltage by sqrt(3). Hence i got my solution.

Please let me know if my method is correct or correct me if i am wrong. Thank you