Hello, I have this project attached and i was trying to understand its whole operation and got stuck.

They're using 4 D-type FFs, and the number of the combination are connected to the Clock inputs, and the data input of the first Flip Flop is connected to GND, so that at the first clock pulse it is reset and its Q output is connected to the Data input of the second Flip Flop so the same happens with the second FF when the Clock input is given by the combination, and continues with the other flip flops, so if the right combination is provided there will be a LOW in the Q output of the last FF, and the transistor is cuttoff because of the specifications in theFF datasheet, it says that it will provide 8.8 mA in the output when it's LOW and using 15V of Vdd, and that's what i dont' understand, why if I give the right combination the transistor will be cuttof? the solenoid won't be activated. By the way, i don't have very much knowledge about solenoids, maybe its operation is not that obvious and that's why i don't understand.

The opposite happens if you enter a wrong combination, because all the other switches are connected to the SET inputs, and no matter the state of the DATa input or the CLOCK it will be HIGH at the Q outputs, and that will turn on the transistor because it will provide -8.8 mA in that output, that means 8.8 mA flowing from outside to inside, right? and that will saturate the transistor, it complements my missunderstanding explained above.

Maybe the right transistor is an NPN, only a guess.

Another question i have is:

What would be the first state of the flip flops before the first Clock pulse is given? SET right? i mean What impedes that i only give the last number of the combination and reset the last flip flop and un lock the system? necesarily a SET i guess.

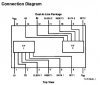

The connection Diagram of theFlip Flop is also attached.

Thanks.

Hope you help me understand this.

They're using 4 D-type FFs, and the number of the combination are connected to the Clock inputs, and the data input of the first Flip Flop is connected to GND, so that at the first clock pulse it is reset and its Q output is connected to the Data input of the second Flip Flop so the same happens with the second FF when the Clock input is given by the combination, and continues with the other flip flops, so if the right combination is provided there will be a LOW in the Q output of the last FF, and the transistor is cuttoff because of the specifications in theFF datasheet, it says that it will provide 8.8 mA in the output when it's LOW and using 15V of Vdd, and that's what i dont' understand, why if I give the right combination the transistor will be cuttof? the solenoid won't be activated. By the way, i don't have very much knowledge about solenoids, maybe its operation is not that obvious and that's why i don't understand.

The opposite happens if you enter a wrong combination, because all the other switches are connected to the SET inputs, and no matter the state of the DATa input or the CLOCK it will be HIGH at the Q outputs, and that will turn on the transistor because it will provide -8.8 mA in that output, that means 8.8 mA flowing from outside to inside, right? and that will saturate the transistor, it complements my missunderstanding explained above.

Maybe the right transistor is an NPN, only a guess.

Another question i have is:

What would be the first state of the flip flops before the first Clock pulse is given? SET right? i mean What impedes that i only give the last number of the combination and reset the last flip flop and un lock the system? necesarily a SET i guess.

The connection Diagram of theFlip Flop is also attached.

Thanks.

Hope you help me understand this.

Attachments

Last edited: