Hi,

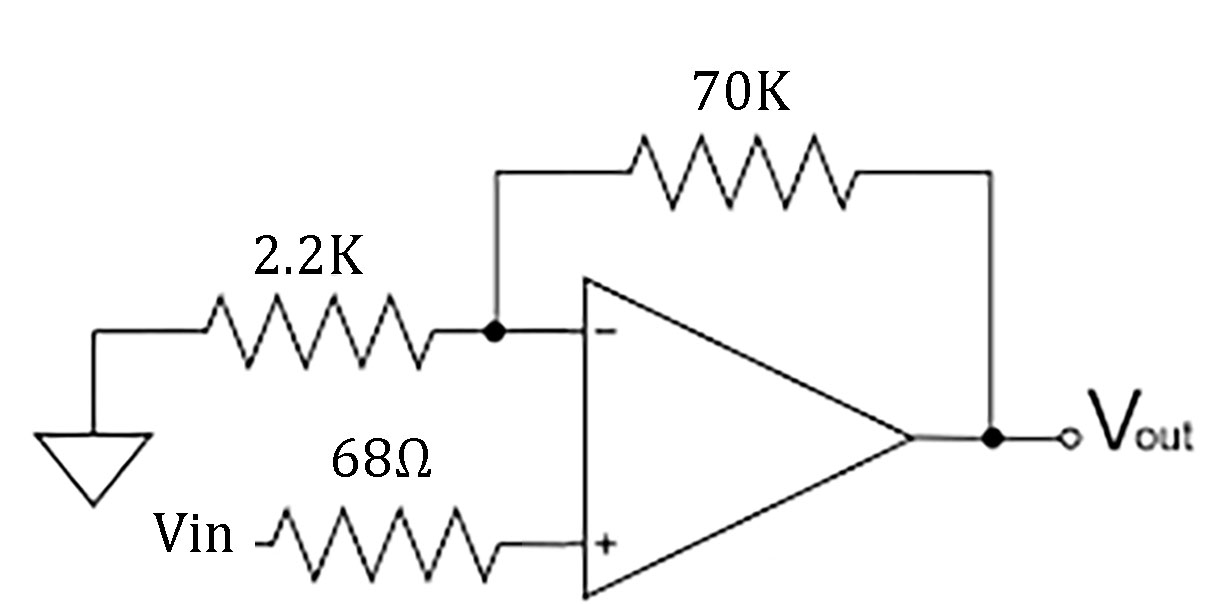

I have 80mVpp 100hz sinusoidal, I have to amplify it to 2Vpp . With -7 +7 opamp power supply. I have made blow circuit :

It works, But I cause distortion in Vin !!! If I change 70K resistor to 40K distortion will solve 100%!

My question is : Do we have effect on +in pin when we use Non-inverter opamp design ? if yes what we have to do to prevent it ?

Master amplifier schematic:

Datasheet

I have 80mVpp 100hz sinusoidal, I have to amplify it to 2Vpp . With -7 +7 opamp power supply. I have made blow circuit :

It works, But I cause distortion in Vin !!! If I change 70K resistor to 40K distortion will solve 100%!

My question is : Do we have effect on +in pin when we use Non-inverter opamp design ? if yes what we have to do to prevent it ?

Master amplifier schematic:

Datasheet

Attachments

Last edited: