Hi,

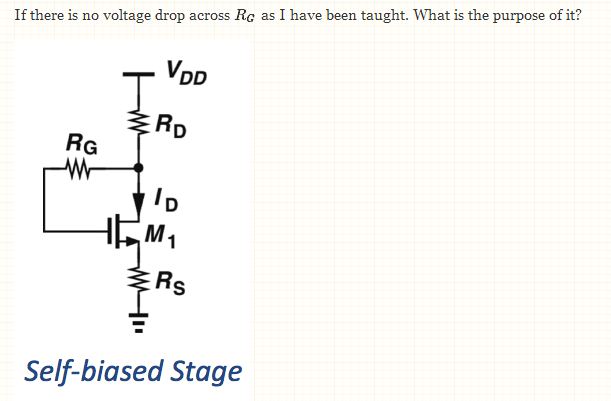

Please help me with this question about self-biased stage of MOSFET.

Here is the answer that I saw in another forum:

How do you get input impedance of MOSFET, [lATEX] R_{D},[/LATEX] if [LATEX]R_{G} [/LATEX]is zero?

For example, if I hook an voltage source Vin to gate of the transistor, thus:

Input impedance of the circuit at gate, Zin:

[LATEX]Z_{in} = \frac{ V_{in} }{I_{in}} = \frac{ V_{in} }{0} = \propto [/LATEX]

To me, it seems that input impedance of the circuit is always infinity. Please point out what/where I am wrong. Thank you.

Please help me with this question about self-biased stage of MOSFET.

Here is the answer that I saw in another forum:

Please help me explain with the highlighted part.Even though there is no voltage drop across RG, it still conveys a voltage to the transistor's gate. If you remove RG, then the gate is floating.

So why not make RG zero ohms? That will also convey the voltage to the gate. However, it will create a low impedance for a signal that is applied to the gate, which will then just be RD ohms away from an AC ground at VDD.

We need a resistor to help maintain whatever input impedance is necessary at the gate.

If you look at the DC picture, it goes something like this. Initially, no current flows through the transistor and so the drain is at VDD. If the drain is at VDD, that means that the gate is also at VDD. But if that's the case, the transistor is actually turned on and so current flows, causing a voltage drop on RD. But, aha, we have feedback! If current flows through RD, then the drain is not in fact at VDD and therefore neither is the gate, so the transistor is not quite as turned on as we thought. The solution to this feedback loop is the operating point, and as you can see, RG is very much involved in it.

How do you get input impedance of MOSFET, [lATEX] R_{D},[/LATEX] if [LATEX]R_{G} [/LATEX]is zero?

For example, if I hook an voltage source Vin to gate of the transistor, thus:

Input impedance of the circuit at gate, Zin:

[LATEX]Z_{in} = \frac{ V_{in} }{I_{in}} = \frac{ V_{in} }{0} = \propto [/LATEX]

To me, it seems that input impedance of the circuit is always infinity. Please point out what/where I am wrong. Thank you.