Hello again,

Yes i agree now. It's almost like an amplifier where the resistor is in the negative feedback path.

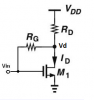

What else is interesting is that with the device biased, with output voltage Vd the input voltage must also be Vd, and with those bias conditions that means the input current is zero (zero through the 1M feedback resistor). I think maybe this was part of what the original question was all about. The input impedance looks infinite, but it's not because as soon as we see some input change we see different operating circumstances and then some real input impedance. Trying to get that condition might be a little hard to do as Rd has to be set with a given Vs to get something that works

Yes i agree now. It's almost like an amplifier where the resistor is in the negative feedback path.

What else is interesting is that with the device biased, with output voltage Vd the input voltage must also be Vd, and with those bias conditions that means the input current is zero (zero through the 1M feedback resistor). I think maybe this was part of what the original question was all about. The input impedance looks infinite, but it's not because as soon as we see some input change we see different operating circumstances and then some real input impedance. Trying to get that condition might be a little hard to do as Rd has to be set with a given Vs to get something that works