Hello!

I am building a digital clock using the schematic on this page:

https://danyk.cz/hodiny2_en.html

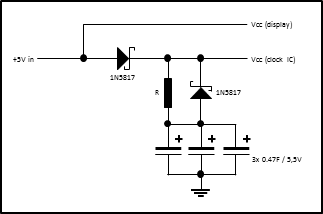

A neat thing to add would be a backup capacitor in case of a power failure, but I have never used these before so I'm not sure how to properly add one to my build. The space available is small width- and heightwise so only a 0.47F fits, but it is however quite long so there is room for up to three 0.47F in a row.

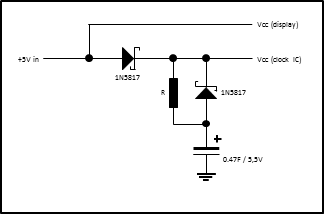

As you can see, my idea is to only have the clock circuit backed up and not the actual LED display.

Hi engineeer,

Welcome to ETO; you will find a lot of people with similar interests to you here.

It would be helpful to us if you could fill in your location on your profile (not your specific address though).

To answer your questions, and I am taking the clock circuit that you have described in the above posts:

Then again, I read somewhere that it isn't always a good idea to parallell supercaps so I wanted to know your thoughts on the matter.

There is absolutely no problem connecting supercaps in parallel. You can evel parallel different values from different manufacturers, provided, of course that you do not exceed the working voltage of any one capacitor in the parallel bank. There are problems connecting any capacitors in series though, not just supercaps.

Also, if my "capacitor circuit" below is correct, how do I calculate a fitting value for R?

Your circuit is correct, although not optimum. The value of R simply defines how long the supercap bank will take to charge back up to its maximum backup voltage, once the mains supply is restored. The minimum time is limited by the current available from your power supply and also by the maximum charging current of the supercap bank. I don't see this as a critical area and the value of R can be calculated quite simply further down the line when more information is available.

The attached Word .doc file shows the calculations for the size of supercap bank you would need to meet your 4 hour backup duration. I have taken spec sheet figures to calculate the total current taken from the supply line by the oscillator and counter chips, and this will probably be pessimistic so you might consider measuring the actual current taken and use that in the equation to arrive at the value of supercap needed. If you have any actual supercap types in mind, it would be handy if you could post a description.

The principle I have used is that the clock chips will operate from a supply line of between 3V and 6V, so 3V is the amount of voltage drop the capacitor can have while still maintaining the oscillator and counter functions.

To use this approach and your circuit, you would need a 6.4V DC supply and an extra diode in line with the 6.4V supply to drop it to 6V, which would be the voltage that the supercap bank would initially supply.

UPDATE: I see that highest voltage that commonly available supercaps will stand is 5.5V, so that will have to be the maximum backup voltage. This implies a maximum backup drop of 5.5V to 3V = 2.5V, rather than 3V as stated in the attached word document.

I have just given the basics of this approach and there may be errors- there normally is with my designs- but this data will allow you to consider the design. No doubt, there will be a few details to sort out.

There are other, more complicated approaches, that would allow you to use a smaller capacitor bank. Also, you could consider using a rechargeable battery, which would be a far superior approach; sorry.

This clock design takes me back to when I built a similar circuit in the 1970s, a counter using the same hp display chips.

spec