Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

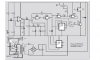

RCA invented Cmos logic ICs a long time ago. They show the analog voltage gain with a 10M feedback resistor and a 1k input resistor at various supply voltages.what is un buffered mean and what's the gain of this amplifier

View attachment 73526

what is un buffered mean and what's the gain of this amplifier

i upload the circuit for more view

View attachment 73526

Magazines simply publish things, they do not design circuits.i find this circuit in epe magazine i suppose it's OK and try to get it

R3? What's the point other than an attempt to make a comparator. With so much gain, it will be pointless.

.

The purpose of resistor R3 is to hold the input high on IC1f, in the absence of a clap signal.

So the output of IC1f is held low and it will not charge C8/R4 via the D3 diode..