Hi,

I am unable to make a voltage controlled constant current source.

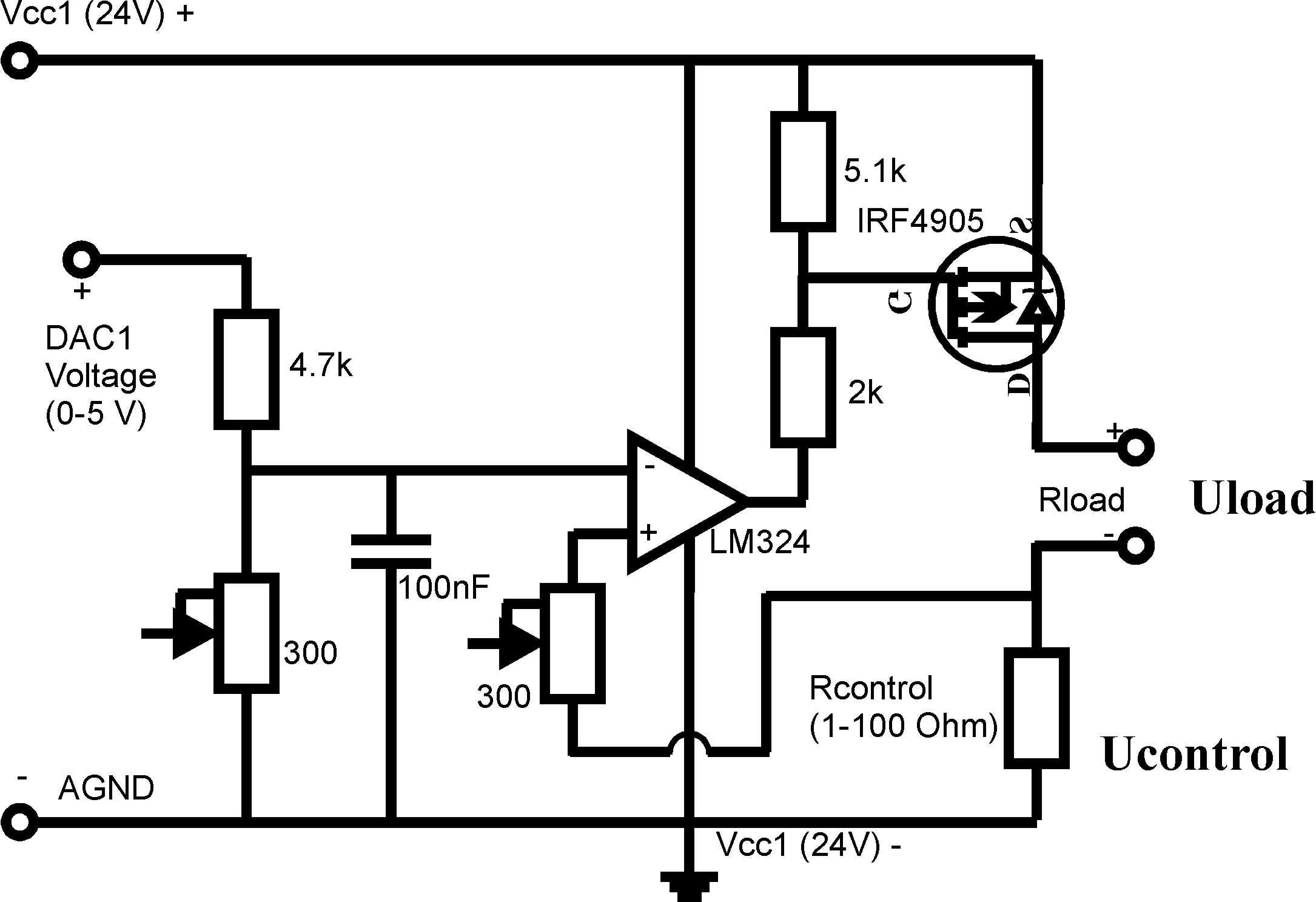

So I am using the following scheme (Sorry for bad sketch drawing):

The constant control voltage varies in the range of 0 to 5 V is applied by constant voltage supply (like HY3002 from e-bay) or (in what follows) by DAC output of PC-controlled board. So the control voltage is rather constant and linear.

The desired output parameters: constant current on load from 0.5 to 150 mA.

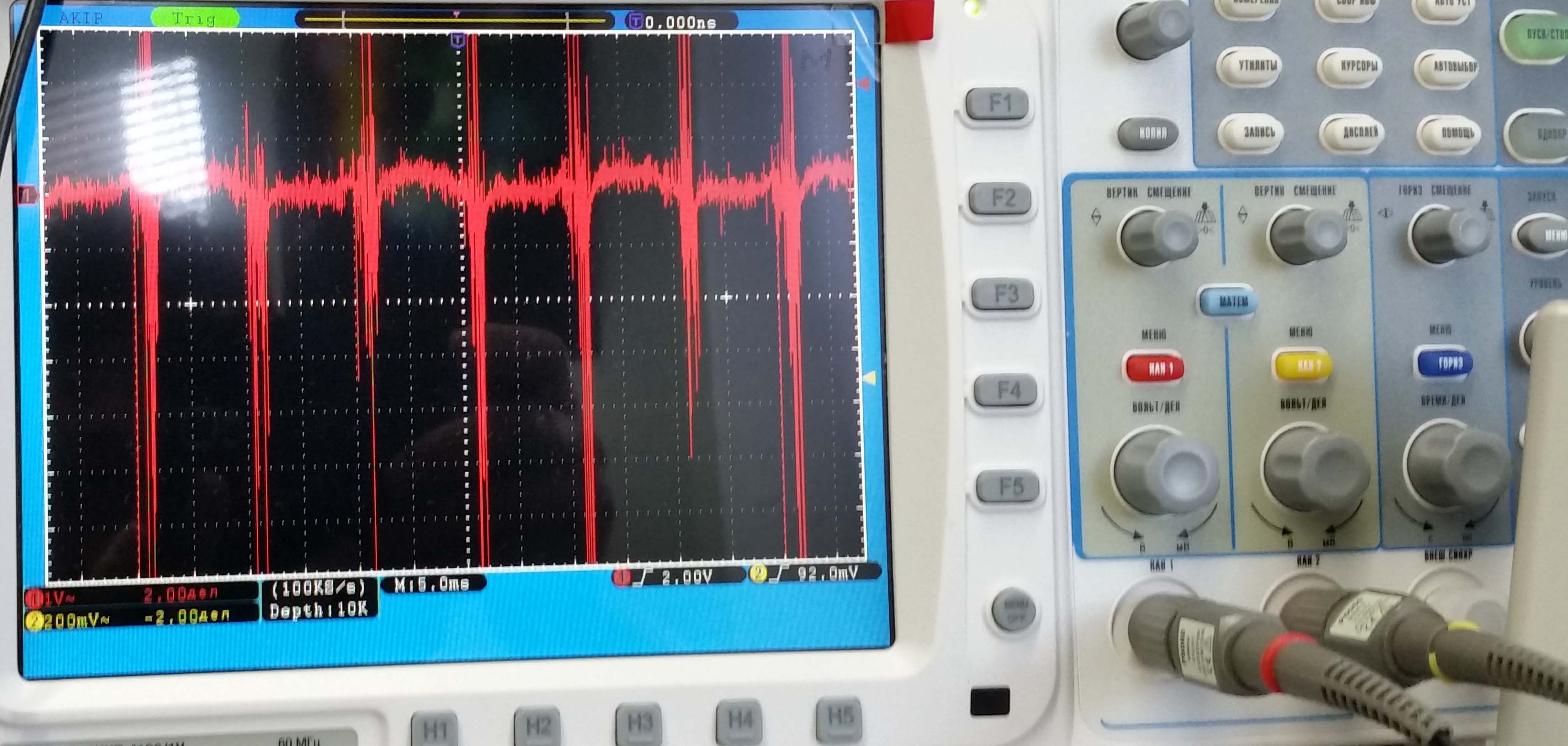

So, as a result, at the load resistance I have got the following signal.

The questions:

What is the source of this large noise in output signal and the signal spikes and drops?

It is possible to tune the scheme to obtain constant current or the used scheme is completely incorrect for constant current supply?

I am unable to make a voltage controlled constant current source.

So I am using the following scheme (Sorry for bad sketch drawing):

The constant control voltage varies in the range of 0 to 5 V is applied by constant voltage supply (like HY3002 from e-bay) or (in what follows) by DAC output of PC-controlled board. So the control voltage is rather constant and linear.

The desired output parameters: constant current on load from 0.5 to 150 mA.

So, as a result, at the load resistance I have got the following signal.

The questions:

What is the source of this large noise in output signal and the signal spikes and drops?

It is possible to tune the scheme to obtain constant current or the used scheme is completely incorrect for constant current supply?