Hi,

I have a requirement to drop a voltage from 5-36V down to 3.3V with precise (0.5%) accuracy. To do this I've used an accurate LDO (RT9050, 5.5V max) and a simple transistor regulator before it. The current draw is minimal, about 20mA max. The circuit was deemed "complete" and is about to be prototyped by a fab house. The one part I didn't check, because it simulated correctly in LTSpice, was the simple transistor regulator part.

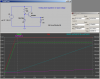

In LTSpice the following screenshot works. I've swapped the transistor out to see how gain affects it but the voltage is stable.

Out of paranoia I built it on a breadboard and found a ~10V increase leads to a 1.5-2V increase on the output. Accuracy increases as the 10K base resistor decreases up to the point enough current is flowing through the zener to make the transistor rather pointless.

Given I have a 36V max input, that's about 6V variance on the output which will blow the precision LDO.

Can anyone explain what's going on, why LTSpice hasn't caught it (LTSpice shows only 0.05V delta between 10 and 30V input)?

Cheers,

Andrew

I have a requirement to drop a voltage from 5-36V down to 3.3V with precise (0.5%) accuracy. To do this I've used an accurate LDO (RT9050, 5.5V max) and a simple transistor regulator before it. The current draw is minimal, about 20mA max. The circuit was deemed "complete" and is about to be prototyped by a fab house. The one part I didn't check, because it simulated correctly in LTSpice, was the simple transistor regulator part.

In LTSpice the following screenshot works. I've swapped the transistor out to see how gain affects it but the voltage is stable.

Out of paranoia I built it on a breadboard and found a ~10V increase leads to a 1.5-2V increase on the output. Accuracy increases as the 10K base resistor decreases up to the point enough current is flowing through the zener to make the transistor rather pointless.

Given I have a 36V max input, that's about 6V variance on the output which will blow the precision LDO.

Can anyone explain what's going on, why LTSpice hasn't caught it (LTSpice shows only 0.05V delta between 10 and 30V input)?

Cheers,

Andrew