Hello everyone,

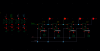

I am trying to design a serial-in parallel-out shift register for my 4-bit DAC. I tried simulating the following circuit but only the first few bits(serial in:01011)are shifting and the rest bits are disappearing. Am I missing something here?

Could someone please let me know what's wrong with it. It would be really helpful.

Thank you

I am trying to design a serial-in parallel-out shift register for my 4-bit DAC. I tried simulating the following circuit but only the first few bits(serial in:01011)are shifting and the rest bits are disappearing. Am I missing something here?

Could someone please let me know what's wrong with it. It would be really helpful.

Thank you