Dear All,

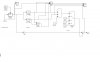

I am trying to implement a 10 bit ADC model in Simulink.

When the input voltage of 5V(sine wave) is provided the outputs obtained on the scope are all 1's(1111111111).When the input is changed to some other value such as 3V the output bits are something different than expected.

As per calculations:

Step size=5V/1023=0.00489.

if for 5 binary has to be 1111111111(1023)

For 3 binary 1001100101(613)

The binary output for 3 I am getting it as 1100110011 which equals to decimal equivalent of 819.

Please correct me what is going wrong in the method

Really need your help.

Thanks in advance.

I am trying to implement a 10 bit ADC model in Simulink.

When the input voltage of 5V(sine wave) is provided the outputs obtained on the scope are all 1's(1111111111).When the input is changed to some other value such as 3V the output bits are something different than expected.

As per calculations:

Step size=5V/1023=0.00489.

if for 5 binary has to be 1111111111(1023)

For 3 binary 1001100101(613)

The binary output for 3 I am getting it as 1100110011 which equals to decimal equivalent of 819.

Please correct me what is going wrong in the method

Really need your help.

Thanks in advance.