Seemed a good idea for my PIC24FV32KA302 project to count up to 60 seconds from a 1Hz input RTC chip ( DS1338) , and each minute to set the timer interrupt. The ISR would display the time and do other time related house work, It worked fine but seemed to have problems when I added an interrupt driven IR input...

You know what thought did , thought wrong... ( my Dad's favourite saying ).

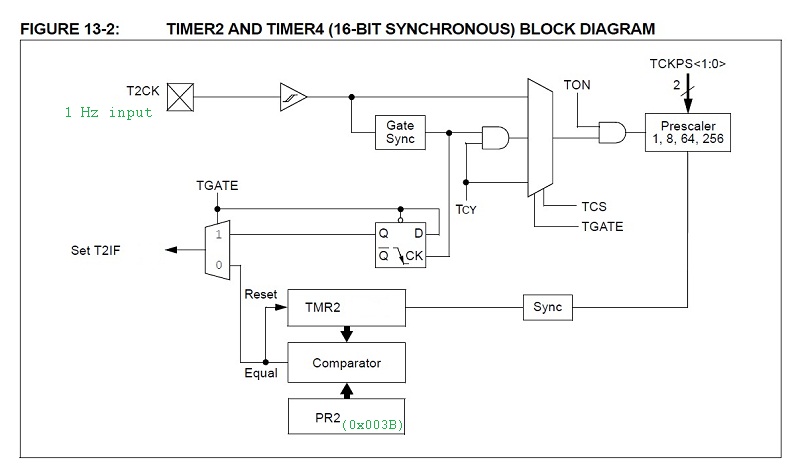

I had not fully understood the PIC's timer 2 operation relating to the reset of the timer count . In normal operation, TMR2 is incremented from 00h on the rise of each clock either FOSC/2 or in my case T2CK pin. Via a 4-bit counter/prescaler, here set to 1:1 to count the 00 to 59 seconds input ( PR2 value) The value of TMR2 is compared to that of the Period register PR2, on each FRC clock cycle. When the two values (TMR2 to PR2 ) match, the comparator generates a match signal as the timer output. This signal resets the value of TMR2 to 00h on the next clock input cycle. Timer2 can also generate an optional device interrupt, the TMR2 Match Interrupt Flag, which is latched in T2IF. So as TMR2 count was not reset for another ½ a second , the compare and T2IF Interrupt continued to be set for all that time and the ISR was called continuously. A simple TMR2=0; code in the ISR fixed my head scratching...

You know what thought did , thought wrong... ( my Dad's favourite saying ).

I had not fully understood the PIC's timer 2 operation relating to the reset of the timer count . In normal operation, TMR2 is incremented from 00h on the rise of each clock either FOSC/2 or in my case T2CK pin. Via a 4-bit counter/prescaler, here set to 1:1 to count the 00 to 59 seconds input ( PR2 value) The value of TMR2 is compared to that of the Period register PR2, on each FRC clock cycle. When the two values (TMR2 to PR2 ) match, the comparator generates a match signal as the timer output. This signal resets the value of TMR2 to 00h on the next clock input cycle. Timer2 can also generate an optional device interrupt, the TMR2 Match Interrupt Flag, which is latched in T2IF. So as TMR2 count was not reset for another ½ a second , the compare and T2IF Interrupt continued to be set for all that time and the ISR was called continuously. A simple TMR2=0; code in the ISR fixed my head scratching...