WTP Pepper

Active Member

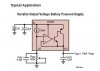

Here is how I would do it:

Using the two Schottky diodes means that only a few nA of current ever flows into/out-of the CMOS input pin. The pin voltage is clamped <5.2V and > -0.2V. The current through the 10K is ~3mA for good noise immunity. Ideally, the CMOS input pin is the kind that has built-in hysteresis.

This is where simulations and real world circuit design drift apart. The V2 logic supply in LTSpice is a clamped hard voltage source. In reality it may consist/likely consist of an NPN pass transistor forward biased to supply (source) the current to a circuit. Think of it like a diving board at a swimming pool. You can pull like hell downwards and it will stay firm. However pushing it up lifts it off its stand easily.

Even with a 10K resistor in series with the 24VAC input, it could reverse bias the pass transistor in the regulator thus causing the voltage to lift where the regulator ceases to work. It cannot sink current due to this reverse biasing of the pass transistor. This can put a high voltage on the rest of the circuit run from the same regulator.

A clamping zener across the output of the regulator would help such lift. A 5.1V zener is stable enough to deal with this as it is the best of both worlds with Zener and Avalanche breakdown.

If you can use a Linear Tech regulator instead of a library voltage source as LT Spice will simulate the problem correctly.