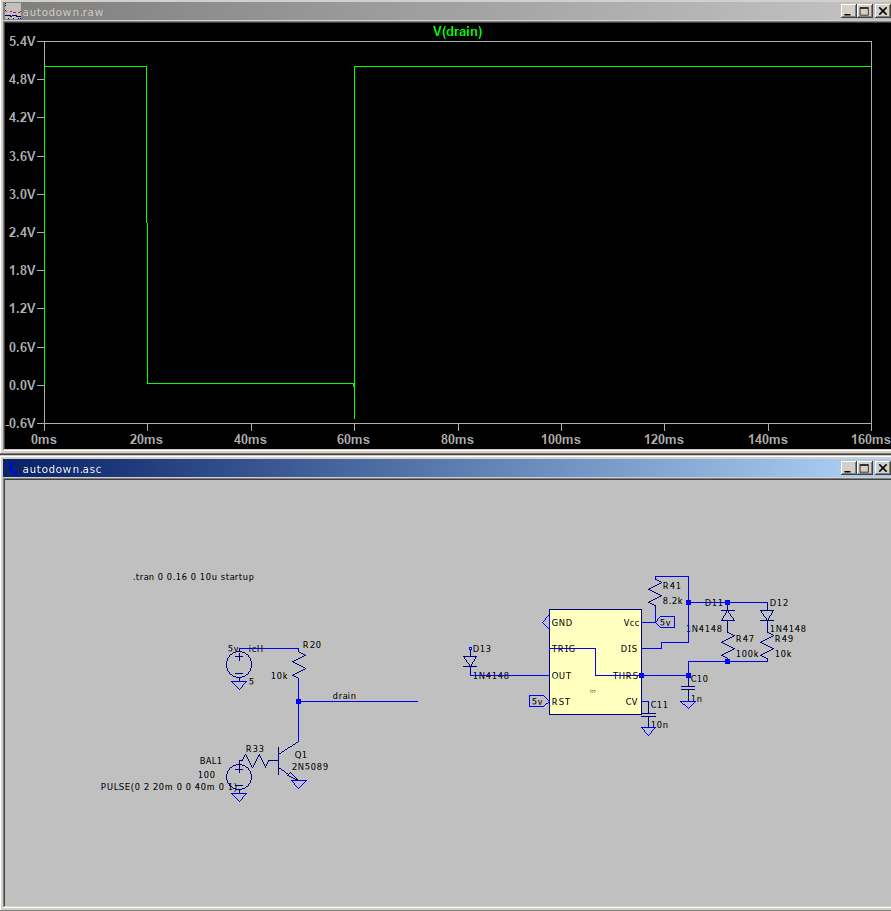

So I have a buck which uses a bootstrap capacitor to switch the high FET. Sometimes I'm forcing reverse flow as a discharge feature and it could be for a while, which unfortunately means I need to blip the signal to the buck to recharge the bootstrap capacitor.

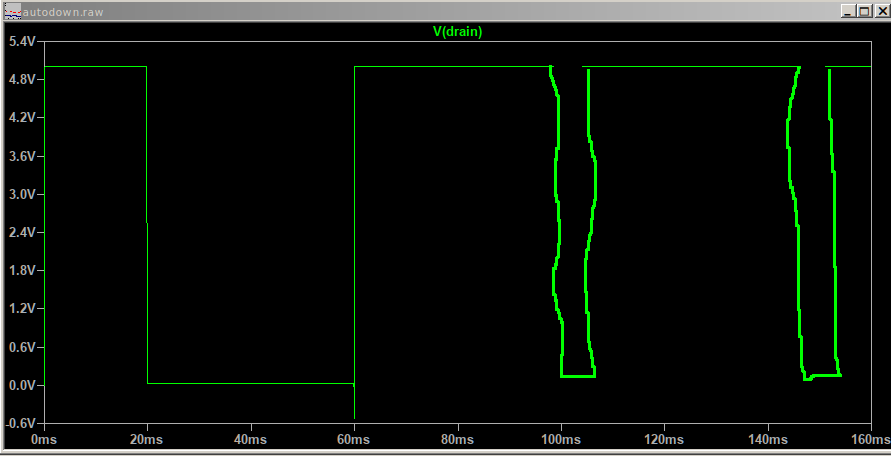

Consider the attached ltspice file. All is well for 60ms, but then there's a period of lengthy high signal. The challenge is to blip the signal twice at around the 100ms and 140ms, just briefly.

So something like..

The drain is a fast PWM signal so whatever reads it must be of high impedance.

It's almost like it needs to be a monostable and an astable but I can't put my finger on it. Be interesting to see what people can come up with!

Consider the attached ltspice file. All is well for 60ms, but then there's a period of lengthy high signal. The challenge is to blip the signal twice at around the 100ms and 140ms, just briefly.

So something like..

The drain is a fast PWM signal so whatever reads it must be of high impedance.

It's almost like it needs to be a monostable and an astable but I can't put my finger on it. Be interesting to see what people can come up with!