Hi,

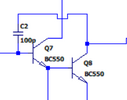

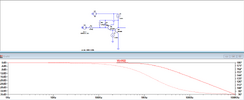

For a school project I had to design a opamp for audio amplification. I now would like to do an ac analysis on just the intermediate stage to see the gain and input impedance yet i am not sure how to simulate this. I remeber a TA talking about adding a feedback resistor that is 0.1 AC 1T but i cant seem to get it to work. The full circuit and the intermediate stage can be seen below. The Emitter current of Q7 is 1A and collector current of Q8 around 2A.

For a school project I had to design a opamp for audio amplification. I now would like to do an ac analysis on just the intermediate stage to see the gain and input impedance yet i am not sure how to simulate this. I remeber a TA talking about adding a feedback resistor that is 0.1 AC 1T but i cant seem to get it to work. The full circuit and the intermediate stage can be seen below. The Emitter current of Q7 is 1A and collector current of Q8 around 2A.