In my quest to design my own an audio power amplifier, I'm trying to fully understand how to design a proper BJT differential amplifier.

I faced two apparently easy questions I cannot answer by myself, even after some hours of thinking about it.

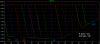

First is about long-tailed pair using resistive loads and 1 mA current source.

Using 8.6k collector resistors, the single ended output Vo1 is nice.

Trying to lower the minimum voltage, I increase the collector resistors to 18,6k.

But now the slope is not linear. There's a change around 0V (marked by a white thick line).

Why is it? Is there any way to solve this?

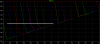

The other issue is about using active loads. Gain is much higher, as expected. But for 0V inputs, the output is almost on its highest value.

Is it well designed? Can I improve this?

Thank you very much!

I faced two apparently easy questions I cannot answer by myself, even after some hours of thinking about it.

First is about long-tailed pair using resistive loads and 1 mA current source.

Using 8.6k collector resistors, the single ended output Vo1 is nice.

Trying to lower the minimum voltage, I increase the collector resistors to 18,6k.

But now the slope is not linear. There's a change around 0V (marked by a white thick line).

Why is it? Is there any way to solve this?

The other issue is about using active loads. Gain is much higher, as expected. But for 0V inputs, the output is almost on its highest value.

Is it well designed? Can I improve this?

Thank you very much!