Hello,

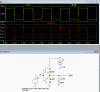

If the digital output (LVCMOS 3V3) is heavily loaded , we may need to use buffer to meet Vih & Ioh (output high current) level of the receiver circuit.

I prefer not use the stand-alone Buffer IC's . Can anyone guide me to design my own buffer circuit based on Transistors ??

Thanks

Antony

If the digital output (LVCMOS 3V3) is heavily loaded , we may need to use buffer to meet Vih & Ioh (output high current) level of the receiver circuit.

I prefer not use the stand-alone Buffer IC's . Can anyone guide me to design my own buffer circuit based on Transistors ??

Thanks

Antony