MacIntoshCZ

Active Member

Hello,

i know some techniques to improve storage time, but not all can be always used.

I would like to see whats inside 10A mosfet driver cause i spend to much time solving this problem.

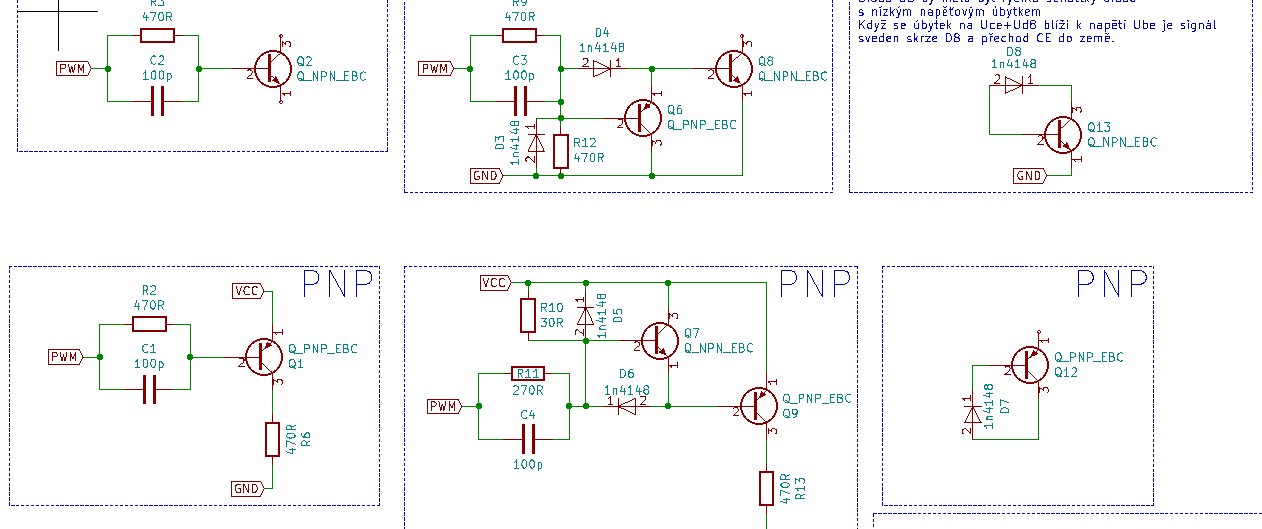

Those i know so far. I do not want to use 10A mosfet driver until i am able to make one myself.

R12 is sometimes a problem. When i have some aplification cause pwm is delivering 10mA, first step is 100mA, then 1A and finnal 10A.

R12 some times need to be low value, but when its too loow it bypassing driving signal... Those schematics are just example. Real schematic is lost (energy distributor failere -> pc turned off, thank you energy distributor =)...), so this would be a shitty question.

Is there any other option to fast turn off transistor from saturation in power electronics?

I am not facing slow turn on, just turn off is problem. I know that instead of 1n4148 schottky should be used.

i know some techniques to improve storage time, but not all can be always used.

I would like to see whats inside 10A mosfet driver cause i spend to much time solving this problem.

Those i know so far. I do not want to use 10A mosfet driver until i am able to make one myself.

R12 is sometimes a problem. When i have some aplification cause pwm is delivering 10mA, first step is 100mA, then 1A and finnal 10A.

R12 some times need to be low value, but when its too loow it bypassing driving signal... Those schematics are just example. Real schematic is lost (energy distributor failere -> pc turned off, thank you energy distributor =)...), so this would be a shitty question.

Is there any other option to fast turn off transistor from saturation in power electronics?

I am not facing slow turn on, just turn off is problem. I know that instead of 1n4148 schottky should be used.

Last edited: