Roff

Well-Known Member

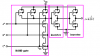

OK, better late than never, I guess. Here's the tardy schematic. Hopefully the two parallel gates will have enough drive for your tach.

EDIT: Corrected error in schematic and added timing diagram. I drew the duty cycle as 20%, since you mentioned that, but it should work with any duty cycle. Note that, at 33.3Hz, there is a component in the output at 8.3Hz, due to the fact that you are dropping every 4th pulse. You may see jitter in the tach at low RPMs.

EDIT: Corrected error in schematic and added timing diagram. I drew the duty cycle as 20%, since you mentioned that, but it should work with any duty cycle. Note that, at 33.3Hz, there is a component in the output at 8.3Hz, due to the fact that you are dropping every 4th pulse. You may see jitter in the tach at low RPMs.

Attachments

Last edited: