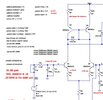

Depending on values, I get insanely optimistic calculations, (.000016% ) I can tweak to probable ( as circuit measured on the bench, more like .003%) or way poor ( .25%)

I have an ongoing project for fun to implement what I learn about class AB amplifier design past the one I built a few year back. I have read what I can understand bout the .tran and .fore statements, but there are some relationships I do not seem to get correct .

For example, if I increase my number of samples( by the time param) I actually get worse results. If I decrease them, they get worse. Not a trend I understand. I think I have the relationship between step and FFT size correct.

I have an ongoing project for fun to implement what I learn about class AB amplifier design past the one I built a few year back. I have read what I can understand bout the .tran and .fore statements, but there are some relationships I do not seem to get correct .

For example, if I increase my number of samples( by the time param) I actually get worse results. If I decrease them, they get worse. Not a trend I understand. I think I have the relationship between step and FFT size correct.