electroRF

Member

Hi,

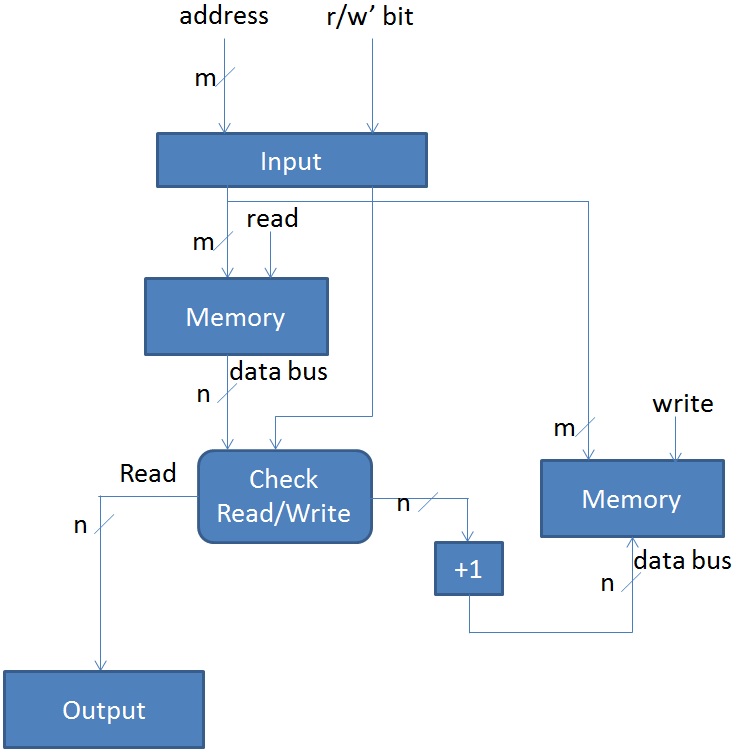

I'm trying to write a block diagram of the following system:

The system gets control bit = r/w'

and it gets m-bit address

when r/w' = 1 (read), it reads the content of that memory address from a memory, and output it on n-data bus.

when r/w' = 0 (write), it reads the content of that memory address from a memory, increment the content by 1, and write it back into the memory address.

The memory itself is given as a black box - no need to design it.

How would you design the rest using Flip-Flops / Mux / Counter / etc (synchronized discrete components)

I sketched it, but I don't know how to translate it into Flip-Flops:

Thank you!

I'm trying to write a block diagram of the following system:

The system gets control bit = r/w'

and it gets m-bit address

when r/w' = 1 (read), it reads the content of that memory address from a memory, and output it on n-data bus.

when r/w' = 0 (write), it reads the content of that memory address from a memory, increment the content by 1, and write it back into the memory address.

The memory itself is given as a black box - no need to design it.

How would you design the rest using Flip-Flops / Mux / Counter / etc (synchronized discrete components)

I sketched it, but I don't know how to translate it into Flip-Flops:

Thank you!