I am reading **broken link removed** from **broken link removed**site. I am uncomfortable with the part Two Flaws of Uncompensated PCMC.

The explanation seems to be contradict with each other.

Please look at the description below.

Here is the author's reasoning:

This seems to be contradict. The author assumed that Vo constant but that assumption leads to increasing of Vo. So this only means that the initial assumption is not correct. And we can not use that assumption to make any conclusion whether the converter indicates poor regulation or not.

Is there something obvious I am missing here?

When Vin drops and duty cycle increases correspondingly the average inductor current keeps constant and only inductor ripple decreases. How does that indicates poor regulation?

The explanation seems to be contradict with each other.

Please look at the description below.

Here is the author's reasoning:

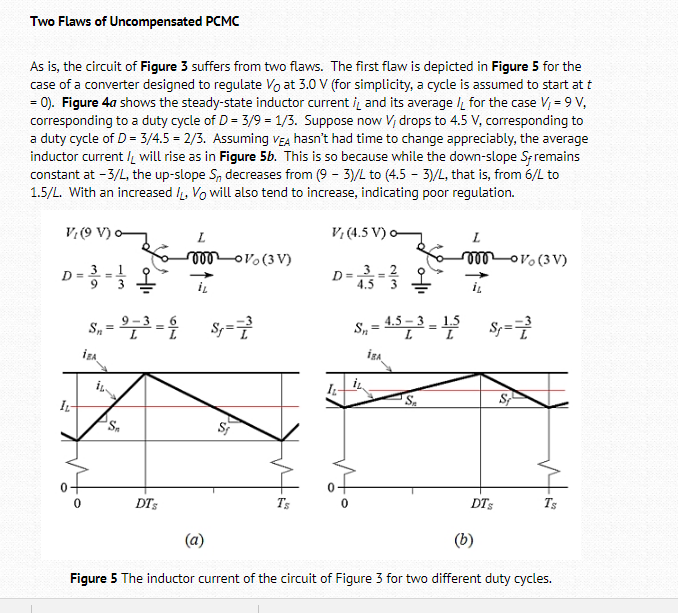

First for the case VI = 9 V, Vo = 3V, corresponding to a duty cycle of D = 3/9 = 1/3.

Now assuming that VI drop to 4.5V, Vo remaining 3V and new duty cycle D = 3/4.5 = 2/3. Also assuming that vEA hasn’t had time to change appreciably.

Then this results in average inductor current iL increases.

However average inductor current increases means that Vo should increase. With an increased IL, VO will also tend to increase, indicating poor regulation.

This seems to be contradict. The author assumed that Vo constant but that assumption leads to increasing of Vo. So this only means that the initial assumption is not correct. And we can not use that assumption to make any conclusion whether the converter indicates poor regulation or not.

Is there something obvious I am missing here?

When Vin drops and duty cycle increases correspondingly the average inductor current keeps constant and only inductor ripple decreases. How does that indicates poor regulation?

Last edited: