hi.

I am looking for a clamper circuit for my system design. I want to use this circuit in my future projects. This circuit already has a positive bias and I want to make this input signal positive clamp.

I made several researches on the Internet, but I could not find exactly what I was looking for. As you know, there are circuits containing various diodes and capacitors. When I applied these circuits, I found that the signal had the lowest voltage of -0.7V negative. However, I do not want my signal to drop to negative voltage.

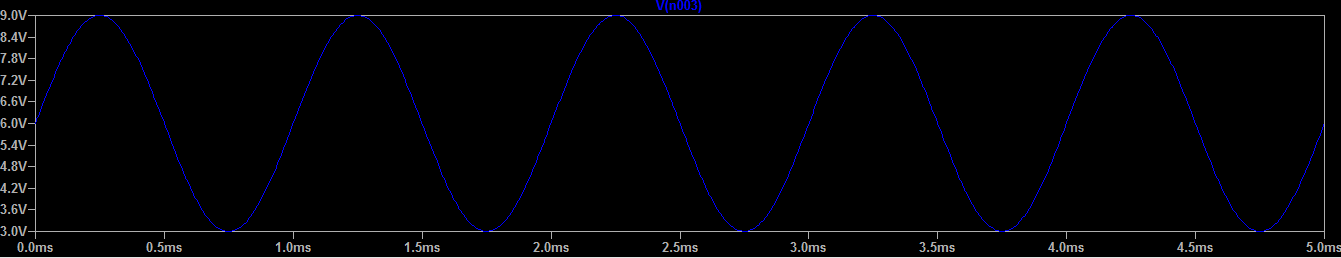

Below I have drawn an example of the signal I have;

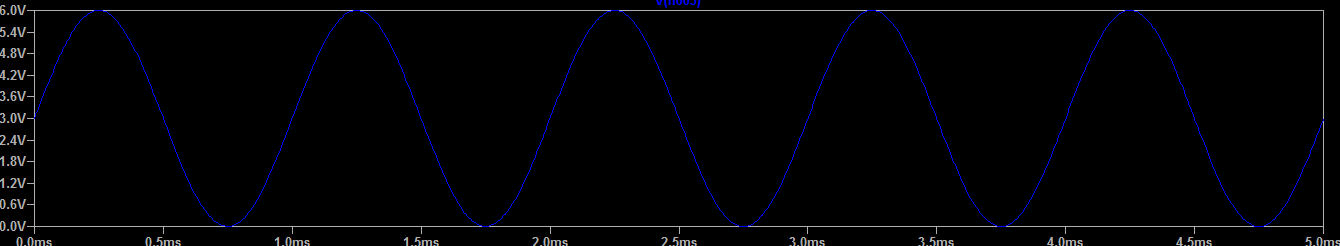

Below I have drawn how the output of the above signal should be;

First of all, I do not have a negative voltage source in my system, so I cannot make negative biasing. For this, I applied to various opamp circuits, but I couldn't find exactly what I was looking for.

Maybe there is a method or notes that you can show me....

I am looking for a clamper circuit for my system design. I want to use this circuit in my future projects. This circuit already has a positive bias and I want to make this input signal positive clamp.

I made several researches on the Internet, but I could not find exactly what I was looking for. As you know, there are circuits containing various diodes and capacitors. When I applied these circuits, I found that the signal had the lowest voltage of -0.7V negative. However, I do not want my signal to drop to negative voltage.

Below I have drawn an example of the signal I have;

Below I have drawn how the output of the above signal should be;

First of all, I do not have a negative voltage source in my system, so I cannot make negative biasing. For this, I applied to various opamp circuits, but I couldn't find exactly what I was looking for.

Maybe there is a method or notes that you can show me....