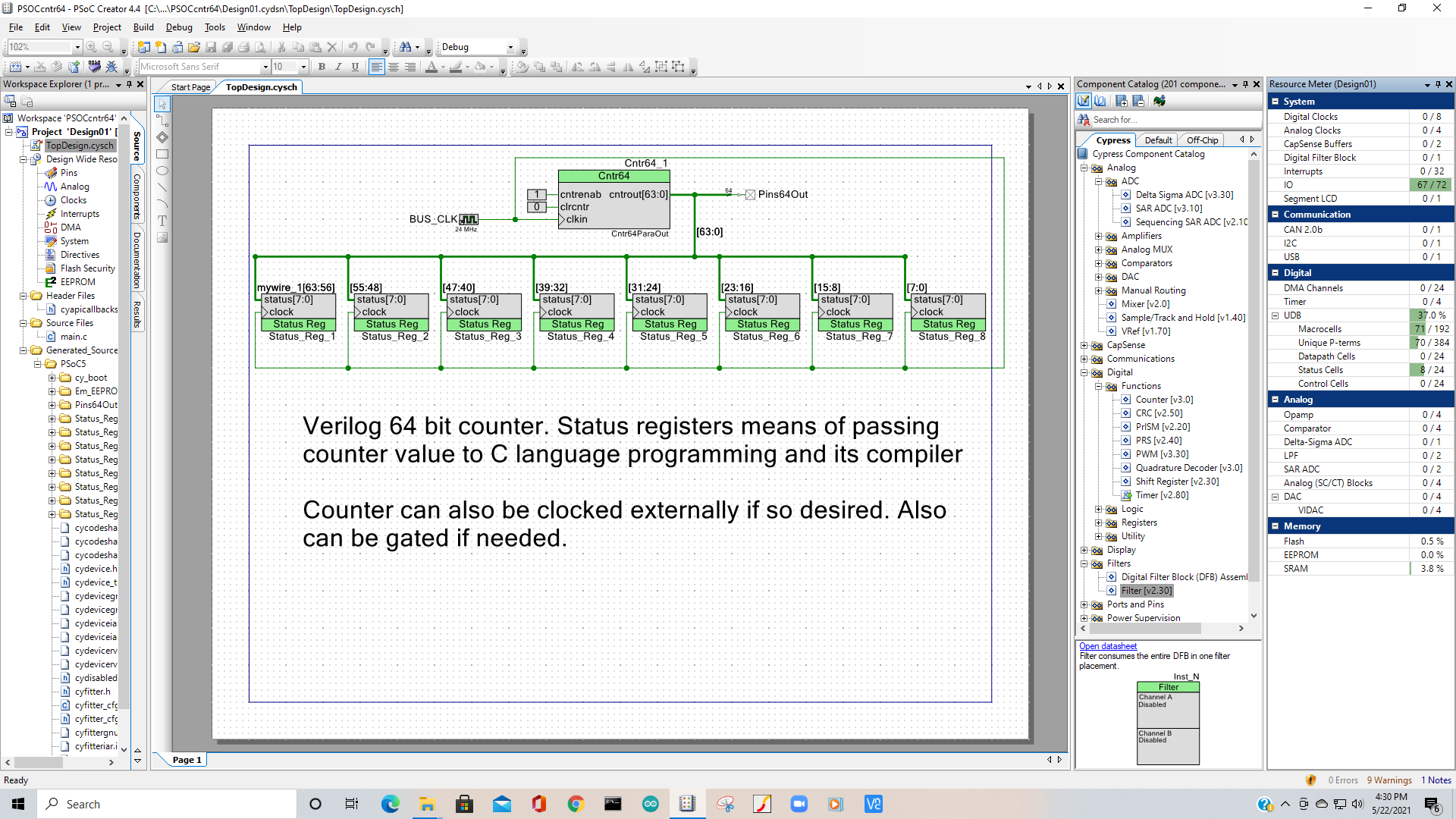

Need a large counter ? This was done in a single chip, done with simple Verilog code. Could

have been done with schematic capture but that would have been tedious.. Notice most of

chip resources un-used, available for other functions. See right hand window. Lots of other

analog and digital resources in the SOC for use.

PSOC 5LP family, Cypress/Infineon. This was a no code design, but ARM core still available

for other stuff. Did a similar design for a SIPO 64 bit shift register. Or quad DDS driving quad

WaveDAC ...Lots of fun.

Tools, PSOC Creator, and compiler free. Typical board for most projects $ 10,

Note, its no C code if you do not use the counter state, just use it by adding internal HW to do a compare

register function. But if you need the cntr value at any point then by definition you are doing a coded design.

Or an ISR on cntr overflow.

Regards, Dana.

have been done with schematic capture but that would have been tedious.. Notice most of

chip resources un-used, available for other functions. See right hand window. Lots of other

analog and digital resources in the SOC for use.

PSOC 5LP family, Cypress/Infineon. This was a no code design, but ARM core still available

for other stuff. Did a similar design for a SIPO 64 bit shift register. Or quad DDS driving quad

WaveDAC ...Lots of fun.

Tools, PSOC Creator, and compiler free. Typical board for most projects $ 10,

Note, its no C code if you do not use the counter state, just use it by adding internal HW to do a compare

register function. But if you need the cntr value at any point then by definition you are doing a coded design.

Or an ISR on cntr overflow.

Regards, Dana.

Last edited: